Состав процессорных устройств

Состав процессорных устройств

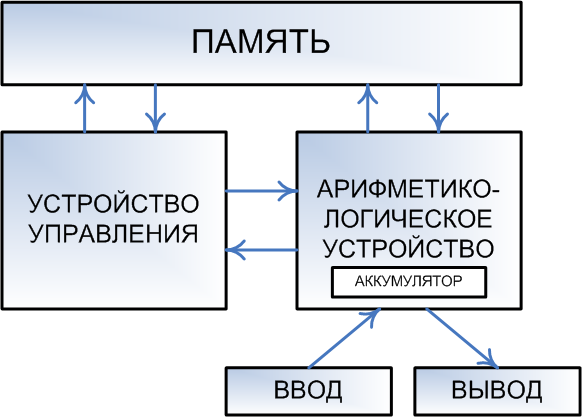

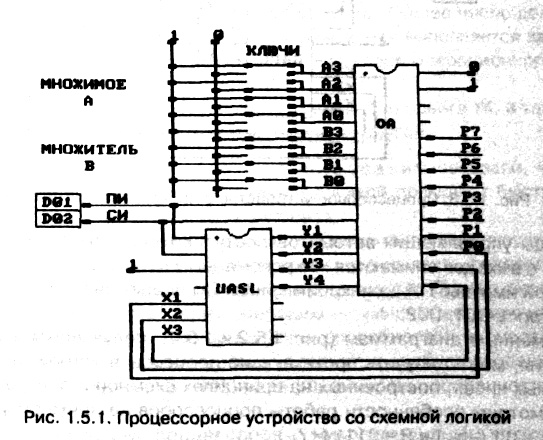

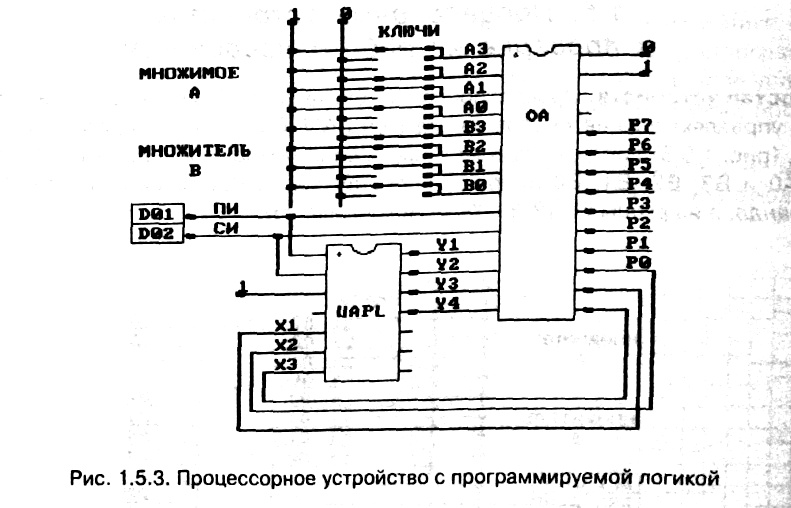

Процессорное устройство составляется из операционного ОА и управляющие автоматов со схемной UASL (рис. 1.5.1) и программируемой UAPL (рис. 1.5.3) логикой, оформленных в виде макромоделей. На входы АЗ, А2, А1, А0 и ВЗ, В2, В1, В0 операционного автомата подаются два 4–разрядных операнда, а на входы Y 1, Y 2, Y З, Y 4 — микрокоманды.

Для установки значений отдельных разрядов множимого А и множителя В используются ключи, с помощью которых каждый из входов АЗ, А2, А1, А0, ВЗ, В2, В1, В0 операционного автомата ОА может быть подсоединен к шине 0 или 1. В исходном состоянии ключи установлены в положение, соответствующее рассматриваемому примеру умножения операндов А = 1011 (–510) и В = 0111 (+710). С выходов операционного автомата снимается произведение в виде 8–разрядного двоичного числа Р7…Р0 и сигналы Х1, Х2, ХЗ логических условий.

На входы управляющих автоматов поступают сигналы Х1, Х2, ХЗ логических условий, а с выходов снимаются микрокоманды Y1, Y2, YЗ.

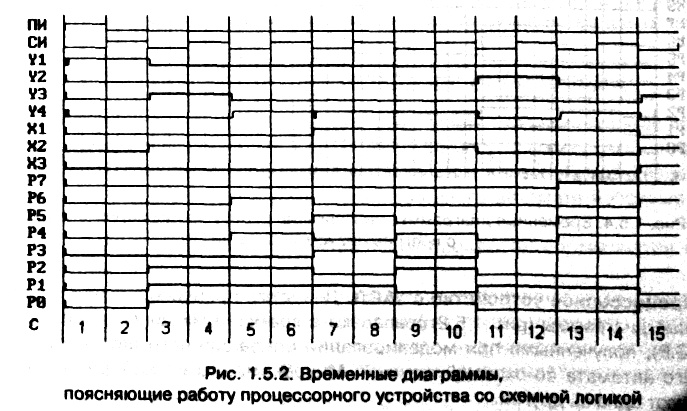

Пусковой импульс ПИ и синхроимпульсы СИ подаются на оба автомата с выхода генераторов D01, D02. По временным диаграммам (рис. 1.5.2 и 1.5 .4), полученным в результате моделирования, можно изучить протекающие процессы в устройствах для умножения двоичных чисел, построенных на принципах схемной и программируемой логики. Рассмотрим особенности работы процессоров на примере умножения операндов А = 1011 (–510) и В = 0111 (+710).

Процессорное устройство с УАСЛ. Для этого процессорного устройства временные диаграммы (рис. 1.5.2) совпадают с временными диаграммами (рис. 1.2.4 и 1.3.6), полученными при моделировании операционного автомата и управляющего автомата со схемной логикой. Микрокоманды из набора Y1, Y2, YЗ, Y4 следуют одна за другой. Операция умножения выполняется за 14 тактов. На такте 15, после того, как логическое условие ХЗ становится равным 1, на выходах OA появляется произведение P7 P6… P0 = 11011101 в дополнительном коде, что соответствует значению –3510.

Процессорное устройство с УАПЛ. Как видно из временных диаграмм (рис. 1.5.4), отражающих работу процессора при использовании управляющего автомата с программируемой логикой, специфика его работы проявляется в том, что на проверку логических условий для выявления следующей выполняемой микрокоманды затрачиваются дополнительные такты. Общее число дополнительных тактов составляет 22. Поэтому операция умножения выполняется за 36 тактов. На такте 37 после выполнения условия ХЗ = 1 с выходов операционного автомата считывается результат Р7Р6…Р0 = 11011101.

Следует отметить, что микрокоманды сложения Y2 и сдвига Y4, а также микрокоманды вычитания Y2 и сдвига Y4 следуют одна за другой.

Результаты компьютерного моделирования показали, что использование управляющего автомата со схемной логикой повышает быстродействие процессорного устройства более чем в два раза.

Изучение структуры в виде операционного автомата и управляющих автоматов со схемной и программируемой логикой позволило выявить основополагающие принципы построения и функционирования процессоров. Однако рассмотренные процессоры выполняют только одну операцию — умножение двоичных чисел по алгоритму Бута. Расширение функциональных способностей процессора связано с увеличением количества выполняемых операций и требует введения дополнительных аппаратных средств. В разделе микропроцессоры рассмотрены особенности процессоров двух типов:

- микропрограммируемых процессоров с микрокомандным управлением. Их функциональные способности определяются системой микрокоманд. Этот тип микропроцессоров программируется на языке микрокоманд и по сути дела является дальнейшим развитием рассмотренной выше структуры из операционного автомата и управляющего автомата с программируемой логикой (рис. 1.4.1);

- программируемых процессоров с командным управлением. Каждая команда представляет собой определенную последовательность микрокоманд. Их функциональные возможности определяются системой команд. Для организации работы процессоров используют программирование на языке команд.

onetwoclick.ru

onetwoclick.ru