Микроконтроллеры (МК) семейства PIC16C5X построены по гарвардской архитектуре, в которой память программ и память данных разделены и имеют собственные адресные пространства.

Микроконтроллеры (МК) семейства PIC16C5X построены по гарвардской архитектуре, в которой память программ и память данных разделены и имеют собственные адресные пространства.

Память программ.

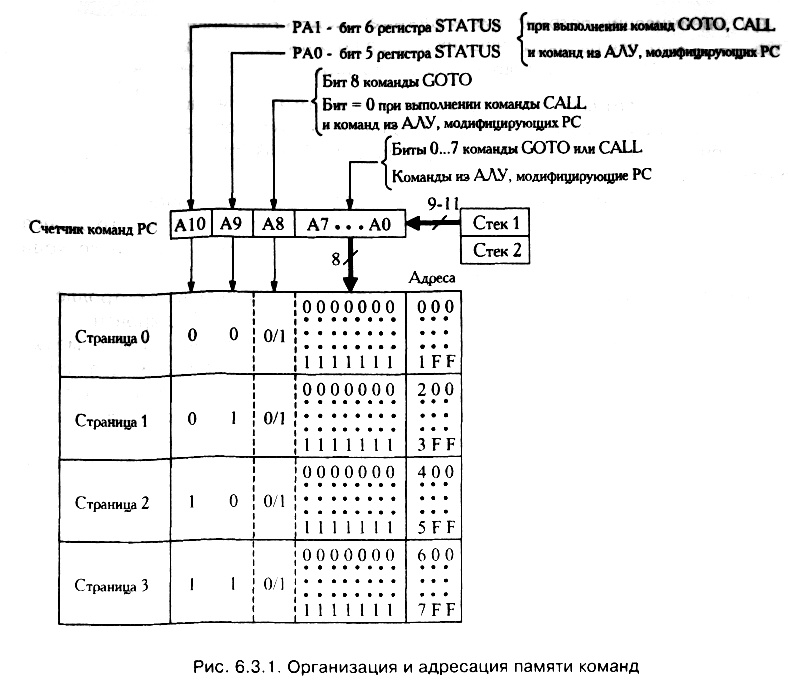

Максимальный объем памяти программ MК PIC16C5X составляет 2048 ячеек по 12 бит. Память программ разбивается на страницы, каждая из которых содержит 512 слов (ячеек). Ранние модели МК имеют всего 512 ячеек памяти программ, относящихся к нулевой странице адресного пространства (рис.6.3.1).

Поэтому разрядность счетчика команд PC равна 9 (А8–А0). В поздних моделях память программ содержит 4 страницы.

Адресация памяти программ

Прямая адресация памяти возможна только в пределах одной страницы, при этом:

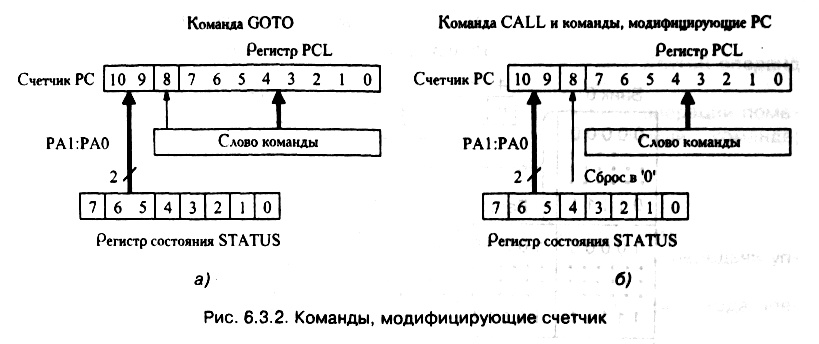

? команда GOTO k (0 ≤ k ≤ 511 ) позволяет обратиться по всем адресам страницы (рис.6.3.2, а);

? команда CALL k (0 ≤ k ≤ 255) и команды, изменяющие содержимое счетчика команд PC, обеспечивают доступ к младшим адресам (0–7) страницы, 8–й бит сбрасывается (рис.6.3.2, б).

Для доступа к памяти свыше 512 ячеек используется, указатель страницы, представляющий собой биты 6 (РА1) и 5 (РА0) регистра состояния (признаков) STATUS процессора (рис.6.2.1).

Для доступа к памяти свыше 512 ячеек используется, указатель страницы, представляющий собой биты 6 (РА1) и 5 (РА0) регистра состояния (признаков) STATUS процессора (рис.6.2.1).

Указатель переключается под управлением программы и реализует по сути дела относительную адресацию.

Память данных

В регистровой памяти МК выделяются две группы регистров:

? специальные регистры, к которым относятся:

• адресуемые 8–разряные регистры (рис.6.3.3, а): псевдорегистр (INDF), регистр таймера/счетчика реального времени (TMR0), регистр счетчика команд (А10, А9, А8, PCL), регистр состояния (STATUS), регистр косвенной адресации (FSR) и регистры ввода/вывода (PORTA, PORTA, PORTC);

• рабочий регистр W, регистр состояния OPTION, регистры управления портами TRISA, TRISB, TRISC (рис.6.3.3, б), доступ к которым осуществляется с помощью специальных команд;

• регистр конфигурации CONFIG, не имеющий доступа.

Информация (выбранный тип генератора, разрешение/запрещение сторожевого таймера и включение/выключение бита защиты от считывания программного кода) в этот регистр заносится на этапе программирования микроконтроллера;

? регистры общего назначения, которые используются программой для хранения переменных по усмотрению пользователя.

Эти 8–разрядные регистры, разделенные на 4 банка по 16 регистров в каждом, и составляют основной объем памяти данных (рис.6.2.2).

Адресное пространство памяти данных объединяет регистры специальных функций и регистры общего назначения.

Специальные регистры и часть регистров общего назначения с адресами 00h.

1Fh отнесены к банку 0.

Поэтому он содержит 32 8–разрядных регистра, в то время как остальных три банка — по 16 регистров.

Для обращения к регистрам в банках 1, 2, 3 выделены соответственно адреса ЗОh.ЗFh, 50h.5Fh, 70h.7Fh.

Таким образом, адресное пространство памяти данных имеет «дыры».

Отметим, что каждый бит любого адресуемого регистра доступен 4 битным командам.

Способы адресации

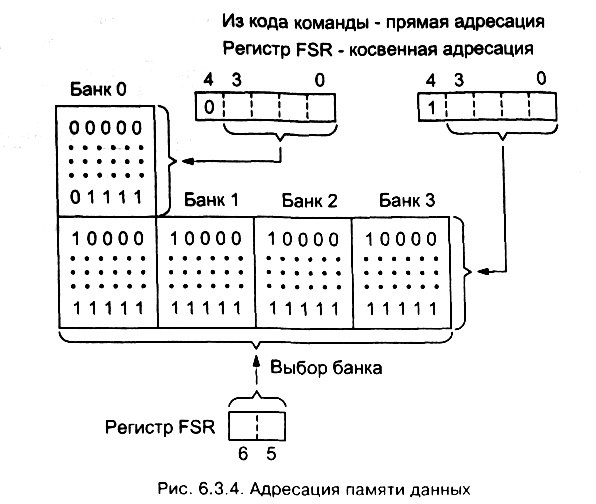

Для обращения к памяти данных (специальным регистрам и регистрам общего назначения) используется косвенная и прямая (относительная) адресация (рис.6.3.4).

Косвенная адресация реализуется с помощью псевдорегистра INDF (физически не существующего, но имеющего адрес 00h) и регистра косвенной адресации FSR (рис.6.3.3, а).

Косвенная адресация реализуется с помощью псевдорегистра INDF (физически не существующего, но имеющего адрес 00h) и регистра косвенной адресации FSR (рис.6.3.3, а).

Псевдорегистр INDF служит указателем регистра FSR, в котором находится адрес запрашиваемого регистра данных: биты 6, 5 задают номер банка (00 — банк 0, 01 — банк 1,10 — банк 2, 11 — банк 3), биты 4.

0 используются для адресации регистра данных внутри банка, при этом:

? бит 4 переключает адрес между 16–ю регистрами первой и второй групп;

? биты 3.

0 адресуют регистры в пределах каждой группы.

Так как в банках 1, 2 и 3 отсутствуют регистры по 16 младшим адресам, при обращении по этим адресам реализуется доступ только к группе регистров банка О с младшими адресами 00h.

Например, при обращении по адресам 23h, 43h, 63h обеспечивается доступ к регистру STATUS, имеющему адрес 03h.

В этих случаях бит 4 регистра FSR автоматически устанавливается в 0, а состояние битов 6 и 5 FSR игнорируется.

При обращении по старшим адресам 10h.

1Fh биты 6 и 5 FSR задают номер банка, а бит 4 устанавливается в единичное состояние (рис.6.3.4).

Прямая адресация обеспечивает доступ только к регистрам банка 0 с помощью младших разрядов кода команд (рис.6.3.4), поступающих по 5–битной шине из дешифратора команд (рис.6.2.1).

Поскольку биты 6 и 5 псевдорегистра FSR действуют постоянно, по сути дела при обращении к страницам 1, 2, 3 осуществляется способ относительной адресации.

onetwoclick.ru

onetwoclick.ru