- Блок последовательного интерфейса.

- Режим 0 (SM0= 0,SM1 = 0)

- Режим 1 (SM0= 0,SM1= 1).

- Режим 2 (SM0 =1,SM1=0).

- Режим 3 (SM0 = 1,SM1 = 1).

- Режим 0 (М1 = 0, М0 = 0).

- Режим 1 (М1 = 0, М0 = 1).

- Режим 2 (М1 = 1, М0 = 0).

- Блок прерываний.

- Назначение и состав блока.

- Уровни прерываний.

- Последовательность обработки прерываний.

Блок последовательного интерфейса.

Блок последовательного интерфейса.

Назначение и состав блока.Блок последовательного интерфейса (БПИ), или последовательный порт,предназначендля организации ввода–вывода последовательных потоков информации.

В состав БПИ входят:

? приемопередатчик,предназначенный для обмена информацией по двухпроводной линии с внешним устройством;

? буферс регистрамиSBUF, обеспечивающий побайтный обмен информацией между внутренней шиной данных МК и приемопередатчиком.

При программировании оба буфера имеют одинаковое имяSBUFи адрес 99h.

Если команда используетSBUFкак регистр источника, то обращение происходит к буферу приемника, если же как регистр назначения, то обращение происходит к буферу передатчика;

? узел управлениядля координации 4–х режимов работы БПИ;

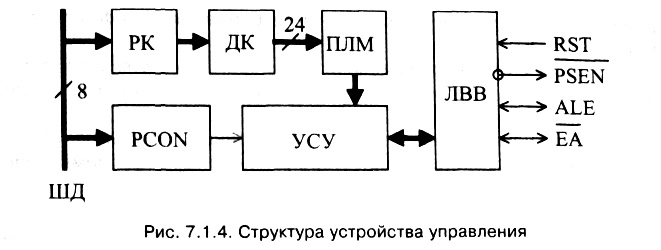

? регистрPCON, имеющий единственный задействованный битSMODв позицииPCON.7 для удвоения скорости передачи данных через последовательный порт.

Остальные биты зарезервированы для дальнейшего использования;

? регистр управления/статусаSCON, назначение разрядов которого приведено в табл.7.1.4.

Все разряды регистра доступны для записи и чтения. Рассмотрим режимы работы блока последовательного интерфейса.

Режим 0 (SM0= 0,SM1 = 0)

В этом режиме БПИ работает как сдвигающий регистр.

Для него характерно следующее: ? информация передается и принимается через вывод порта Р3.0 (используемый обычно как вход приемникаRxD).

Формат посылки — 8 бит;

? каждый передаваемый и принимаемый бит посылки синхронизируется импульсами (стробами) с частотойFOSC/12 (FOSC— частота тактового генератора), передаваемыми через вывод порта Р3.1(используемый обычно как выход передатчикаTxD).

Схема и временные диаграммы, иллюстрирующие работу последовательного порта в режиме 0, приведены на рис.7.1.14.

ПЕРЕДАЧА активизируется любой командой, которая использует буфер передатчикаSBUFв качестве регистра назначения.

ПЕРЕДАЧА активизируется любой командой, которая использует буфер передатчикаSBUFв качестве регистра назначения.

При выполнении такой команды в фазеS6P5 аппаратно вырабатывается импульс «Запись вSBUF»,по которому:

? предназначенный для передачи байт данных черезSBUFзаносится в регистр сдвига передатчика;

? запускается блок управления передатчиком.

Через один полный машинный цикл аппаратно вырабатывается сигнал «Посылка» = 1.

разрешающий выдачу битаD0 из регистра сдвига передатчика на выходRxDи импульсов «СдвигTxD»на выходTxDпорта. Импульсы «СдвигTxD»в состояниях S3,S4, S5имеют низкий уровень, в состоянияхS6, S1, S2— высокий.

Их можно использовать для синхронизации внешних устройств. При сигнале «Посылка» = 1 в фазеS6P2каждого машинного цикла аппаратно формируется импульс «Сдвиг», по которому содержимое передатчика смещается на один разряд вправо и на выходеRxDпоявляется очередной бит данных.

Освободившийся старший разряд регистра сдвига передатчика заполняется нулевым битом, который передается в детектор нуля.

При получении от детектора нуля (после 8–го импульса «Сдвиг») сигнала «Передатчик пуст» блок управления в фазеS1P1снимает сигнал «Посылка» и устанавливает флаг прерывания передатчикаTIв регистре управленияSCON.

ПРИЕМ начинается при одновременном выполнении двух условий:

? должен быть установлен бит разрешения приема последовательных данных(REN= 1) в регистре управленияSCON;

? должен быть сброшен флаг прерывания приемника (RI= 0) в регистреSCON.

На рис. 7.1.14, б показаны процессы при приеме после подачи сигнала «Запись вSCON»,сбрасывающего флагRI.

В фазе S6P2 следующего машинного цикла узел управления приемником аппаратно вырабатывает сигнал «Прием» = 1, разрешающий выдачу импульсов «СдвигTxD»на выходTxDпоследовательного порта.

Так же как и при ПЕРЕДАЧЕ, импульсы «СдвигTxD»в состояниях S3,S4, S5имеют низкий уровень, в состоянияхS6, S1, S2— высокий.

Биты принимаемой посылки через входRxD,состояние которого опрашивается в фазеS5P2каждого цикла, поступают в регистр сдвига приемника.

При сигнале «Прием» – 1 в фазеS6P2каждого машинного цикла аппаратно формируется импульс «Сдвиг», по которому содержимое сдвигающего регистра приемника сдвигается на один разряд влево.

Освободившийся младший разряд заполняется следующим битом данных, поступающим со входаRxD.

После 8–го импульса «Сдвиг» в узле управления приемником формируется сигнал «ЗагрузкаSBUF»,по которому содержимое сдвигающего регистра переписывается в буфер приемникаSBUF.

В фазеS1P110–го машинного цикла после сигнала «Запись вSCON»происходит сброс сигнала «Прием» («Прием» = 0) и установка флага прерывания приемника(RI= 1) в регистреSCON.

Схема и временные диаграммы, иллюстрирующие работу врежимах1, 2, 3 приведены на рис. 7.1.15.

Схема и временные диаграммы, иллюстрирующие работу врежимах1, 2, 3 приведены на рис. 7.1.15.

В этих режимах БПИ работает какуниверсальный приемопередатчик.В передатчике и приемнике используются 9–разрядные регистры сдвига.

Режим 1 (SM0= 0,SM1= 1).

Информация передается через вывод Р3.1 порта Р3 (выход передатчикаTxD),принимается — через вывод Р3.0 (вход приемникаRxD).Формат посылки — 10 бит: нулевой старт–бит, 8 бит данных, единичный стоп–бит.

В этом режиме сигналы синхронизации передачи (СИ Тх) и приема (СИRx)формируются путем деления на 16 или 32 (соответственно при значениях битаSMOD= 1 иSMOD= 0 регистраPCON)частотыFT/C1импульсов, поступающих с выхода таймера–счетчика T/C1.

Период синхронизации определяет время трансляции бита, т.е. его нахождение на выводахTxDилиRxDпорта. Поэтому частота передачи и приема задается таймером–счетчиком T/C1 и составляетFT/C1/16илиFT/C1/32.

ПЕРЕДАЧА активизируется (так же как и в режиме 0) любой командой, которая использует буфер ПередатчикаSBUFв качестве регистра назначения.

При выполнении такой команды аппаратно в фазеS6P5 вырабатывается импульс «Запись вSBUF»,по которому:

? предназначенный для передачи байт данных черезSBUFзагружается в регистр сдвига передатчика;

? в 9–й разряд регистра сдвига передатчика заносится стоп–бит (1);

? запускается блок управления передатчиком.

Однако активный сигнал «Посылка#» = 0, который инициирует начало передачи, формируется только с приходом первого синхроимпульса «СИ Тх» в фазеS1P1машинного цикла.

Первым из узла управления передатчиком через логические элементы И и ИЛИ на выходTxDпоступает нулевой старт–бит.

С приходом второго синхроимпульса «СИ Тх» формируется сигнал «Данные» = 1 для разрешения передачи битов данных и девяти импульсов «Сдвиг».

По фронту сигнала «Данные» из регистра сдвига передатчика на выходTxDвыводится бит данныхD0.

Вывод последующих бит данных происходит с помощью импульсов «Сдвиг», которые формируются под действием каждого синхроимпульса «СИ Тх».

По сигналу «Передатчик пуст», формируемого детектором нуля после 9–го импульса «Сдвиг», узел управления передатчиком устанавливает флаг прерывания передатчикаTI= 1 и снимает сигналы «Посылка#» и «Данные».

Для ПРИЕМА (битREN= 1 в регистреSCON) данных по последовательному каналу в детекторе перепада 16 раз за период синхроимпульсов «СИRx»(с частотойFT/C1илиFTC1/2)с помощьюсигнала «ОпросRxD»производится опрос входа приемника.

При обнаружении перехода сигнала на входеRxDиз 1 в 0 (появлении старт–бита со стороны внешнего устройства), происходит сброс и новый запуск счетчика–делителя на 16 в цепи синхронизации, после чего начинается прием отдельных бит байта данных.

Счетчик–делитель позволяет фиксировать 16 состояний (фаз) принимаемого бита.

В состояниях 7, 8, 9 детектор бит с помощью сигнала «Опрос 7–9» считывает с входаRxDтри значения принимаемого бита, по мажоритарному принципу «2 из 3–х» выбирает одно значение и передает его на вход регистра сдвига приемника.

При этом узел управления приемника аппаратно формирует импульс «Сдвиг», в результате чего принятый бит заносится в сдвигающий регистр приемника и его содержимое сдвигается на один разряд в сторону старших разрядов.

После 10–го импульса «Сдвиг» сдвигающий регистр приемника заполняется и его восемь бит данныхD0–D7по сигналу «ЗагрузкаSBUF»загружаются в буферный регистр приемника, A стоп–бит — в разрядRB8регистра управленияSCONи устанавливается флаг прерывания приемникомRI= 1.

Сигнал «ЗагрузкаSBUF»,битыRB8иRIвырабатываются блоком управления, если в момент формирования 10–го импульса «Сдвиг» выполняются следующие условия: 1.RI= 0; 2. либоSM2= 0, либо стоп–бит равен 1.

Если хотя бы одно из условий не выполняется, флагRIне устанавливается, A принятая посылка безвозвратно теряется.

Если при приеме старт–бита (первого бита посылки) детектор бит в результате мажоритарного отбора выдает 1 вместо 0, все устройства приемника сбрасываются и начинается отслеживание перехода сигнала из 1 в 0 на входеRxD.Таким образом обеспечивается защита от сбойных старт–битов.

Режим 2 (SM0 =1,SM1=0).

Информация передается через вывод Р3.1 порта Р3 (выход передатчикаTxD),принимается — через вывод Р3.0 (вход приемникаRxD).

Формат посылки — 11 бит: нулевой старт–бит, 8 бит данных, программируемый 9–й бит (бит ТВ8 регистраSCONпри передаче, битRВ8 регистраSCONпри приеме), единичной стоп–бит.

частота передачи и приема задается программно и составляетFOSC/32 илиFOSC/64.

Помимо частоты синхронизации отличие режима 2 от режима 1 проявляется в том, что (см. рис.7.1.15, а):

? данные содержат девять бит;

? при ПЕРЕДАЧЕ в регистр сдвига передатчика и детектор нуля по сигналу «Запись вSBUF»засылается программируемый 9–й бит ТВ8;

? при ПРИЕМЕ вместо стоп–бита фигурирует принятый в посылке 9–й битRB8.

Режим 3 (SM0 = 1,SM1 = 1).

Этот режим отличается от режима 2 лишь тем, что частота передачи и приема задается таймером–счетчиком T/C1 (как в режиме 1).

Особенности работы в мультипроцессорных системах.В регистре управления/статусаSCONпоследовательного интерфейса битSM2 (позицияSCON.5) позволяет в режимах 2 и 3 приемопередатчика простыми средствами организовать обмен информацией между микроконтроллерами в локальных управляющих сетях.

В указанных режимах приSM2 = 1 флаг прерывания приемникаRIне активизируется, если девятый битRB8 принятых данных равен 0.

Поэтому для межпроцессорного обмена передаетсяRB8 = 1, чтобы при получении стоп–бита вызвать прерывание приемника установкой флагаRI= 1.

Рассмотрим последовательность передачи данных ведущим микроконтроллеромMК одному или нескольким ведомым.

Ведущий МК в «широковещательном» режиме, когда работают все ведомые МК, посылает байт–идентификатор абонента (адресный код получателя), который отличается от байта данных наличием 1 в девятом разряде.

При получении байта–идентификатора все ведомые МК входят в режим прерывания и вызывают подпрограмму сравнения байта–идентификатора с кодом собственного сетевого адреса.

Микроконтроллер, собственный адрес которого совпадает с принятым байтом–идентификатором, производит сброс битаSM2и переходит к приему данных от ведущего МК.

Остальные ведомые МК, адреса которых не совпадают с кодом байта–идентификатора, сохраняют значение битаSM2= 1 и передают управление основной программе.

Блок таймеров/счетчиков.

Блок таймеров/счетчиков.

Блок таймеров–счетчиков (T/C) относится к средствам поддержки режима реального времени и предназначен для подсчета числа внешних событий, получения программно управляемых временных задержек, выполнения времязадающих функций МК и других целей.

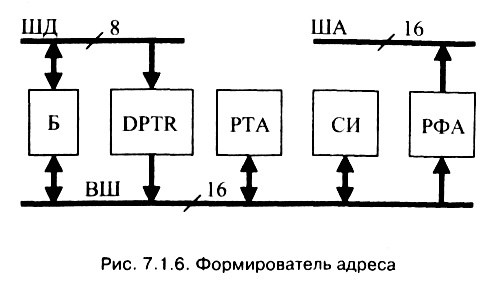

В состав блока таймеров/счетчиков входят (рис.7.1.16):

? буферБ для связи ШД с внутренней шиной блока;

? два 16–разрядных таймера–счетчикаT/C0, T/C1, предназначенные для хранения содержимого счета.

Каждый из Т/Cn(n= 0, 1) состоит из пары восьмиразрядных регистров ТН0, ТН1 (старшие 8 разрядов) иTL0, TL1(младшие 8 раз–рядов);

? схема инкрементаСхИ для увеличения на 1 содержимого: • регистровTC0,ТС1 (в каждом машинном цикле), для которых установлен режим таймера и счет разрешен; • регистровTC0,ТС1, для которых установлен режим счетчика, счет разрешен и на соответствующем входе Т0 или Т1 МК зафиксирован счетный импульс;

? схема фиксации ?INT0, ?INT1, Т0, Т1, состоящая из четырех триггеров, предназначенных для запоминания сигналов ?INT0, ?INT1, Т0, Т1 в моментS5P2 каждого машинного цикла;

? схема управления флагами,устанавливающая и снимающая флаги переполненияTFи флаги запросов внешних прерыванийIE;

? узел управленияT/C, синхронизирующий работу регистров T/C0, T/C1 в соответствии в запрограммированными режимами;

? восьмиразрядныйрегистр режимовTMODдля хранения кода, который задает режимы работыTC0,ТС1, причем разряды (биты) 0…3 определяют режим работыTC0, Aразряды 4…7 — ТС1.

Назначение разрядовTMOD приведено в табл.7.1.5;

? восьмиразрядныйрегистр управленияTCON, который предназначен для приема и хранения кода управляющего слова (табл.7.1.6).

Режимы 0, 1, 2 одинаковы для T/C0 и T/C1.

Режимы 0, 1, 2 одинаковы для T/C0 и T/C1.

Поэтому особенности работы в этих режимах проиллюстрируем на примере T/C0.

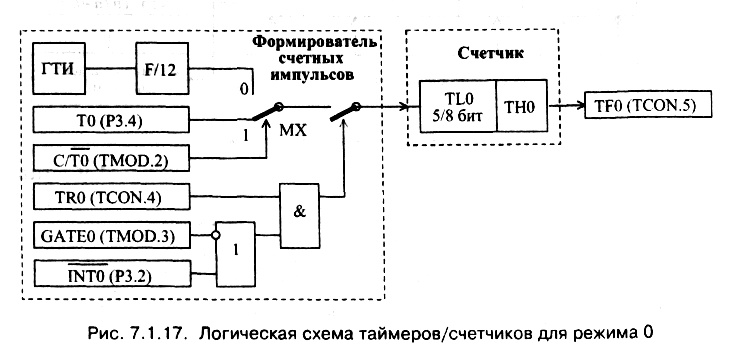

Режим 0 (М1 = 0, М0 = 0).

Режим 0 (М1 = 0, М0 = 0).

Логическая схема для этого режима приведена на рис.7.1.17.

В ее состав входят формирователь счетных импульсов и 13–разрядный счетчик, образованный из регистра ТН0 и 5 младших разрядов регистра ТL0).

Сигнал переполнения (переход из состояния «все единицы» в состояние «все нули») счетчика фиксируется установкой флагаTF0 = 1 в разряде 5 регистра управленияTCON.

Счет разрешается приTR0 = 1,GATE0= 0 илиTR0=1, ?INT0 =1.

Бит С/?Т0, поступающий на адресный вход мультиплексора из регистра режимовTMOD, задает для ТС0 функцию таймера (С/?Т0 = 0) или счетчика (С/?Т0 = 1 ).

Функциятаймерасостоит в счете импульсов, следующих с частотойFOSC/12.

При функционировании ТС0 в качествесчетчикавнешних событий ведется подсчет числа переходов из 1 в 0 на входе Т0.

При этом вход ТС0 аппаратно проверяется в фазеS5P2 каждого машинного цикла.

Если в текущем машинном цикле Т0 = 1, A в последующем Т0 = 0, то содержимое счетчика увеличивается на 1 и фиксируется в фазеS3P1 нового машинного цикла.

Поскольку процедура обнаружения перехода из 1 в 0 длится два машинных цикла, максимальная частота счета не должна превышатьFOSC/24.

Каждый уровень (1 или 0) на входе Т0 должен удерживаться не менее одного машинного цикла.

Режим 1 (М1 = 0, М0 = 1).

Отличие режима 1 от режима 0 обусловлено лишь тем, что в счетчике используются все восемь разрядов регистра ТL0 (рис.7.1.17).

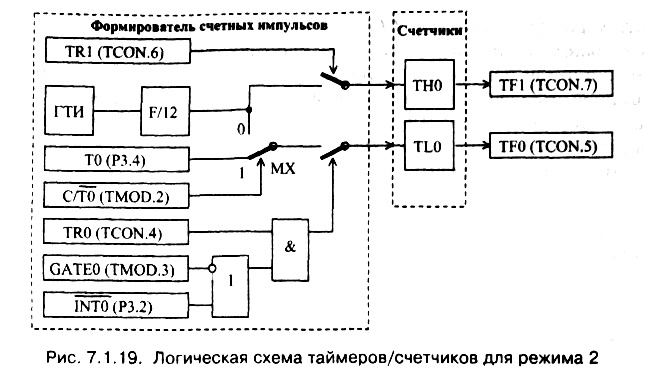

Режим 2 (М1 = 1, М0 = 0).

В этом режиме переполнение 8–битного счетчика ТL0 приводит не только к установке флага переполнения ТF0 (рис.7.1.18), но и к перезагрузке ТL0 содержимым регистра ТН0, которое предварительно было задано программным путем.

Режим 3(М1 = 1, М0 = 1).

Режим 3(М1 = 1, М0 = 1).

В этом режиме задействован только таймер–счетчик ТС0, который можно представить как два независимых устройства (рис.7.1.19).

В первом устройстве в качестве счетчика используется регистрTL0.

Принцип его работы такой же, как и в режиме 0.

Второе устройство выполняет только функции таймера.

Его счетчик построен на регистре ТН0. Включение счетчика осуществляется битомTR1, A для фиксации переполнения используется флагTF1.

Установка ТС1 в режим 3 приводит к блокировке регистровTL1,TH1 с сохранением их содержимого.

Установка ТС1 в режим 3 приводит к блокировке регистровTL1,TH1 с сохранением их содержимого.

Блок прерываний.

Назначение и состав блока.

Блок прерыванийпредназначендля организации системы прерывания программ.

Он обеспечивает поддержку прерываний от пяти источников: ?от флаговIE0,IE1 регистра управленияTCON(см.табл.7.1.6), инициируемых внешними сигналами запросаINT0,INT1;

? от флаговTF0,TF1 регистраTCON, устанавливаемых при переполнении таймеров/счетчиков T/C0, T/C1;

? от флага прерывания передатчикаTIили приемникаRIрегистра управленияSCON(см.табл. 7.1.4) последовательного порта.

В состав блока прерываний входят (рис.7.1.20):

В состав блока прерываний входят (рис.7.1.20):  ?буферБ, обеспечивающий обмен информацией между шиной данных МК и внутренней шиной блока прерываний;

?буферБ, обеспечивающий обмен информацией между шиной данных МК и внутренней шиной блока прерываний;

? схемавыработки вектора прерыванияСВВ, формирующая двухбайтовые адреса подпрограмм обслуживания прерывания;

? узелуправления;

?регистр управления/статуса SCON (табл.7.1.4);

? регистр управления/статусаТСОN (табл.7.1.6);

? регистр разрешения(маскирования)прерыванийIE, предназначенный для разрешения или запрещения прерывания для каждого из пяти источников прерываний.

Назначение отдельных битов регистра приведено в табл.7.1.7;

? регистр приоритетов прерыванийIP, предназначенный для установки уровня приоритета прерывания для каждого из пяти источников прерываний.

Назначение отдельных битов регистра приведено в табл.7.1.8.

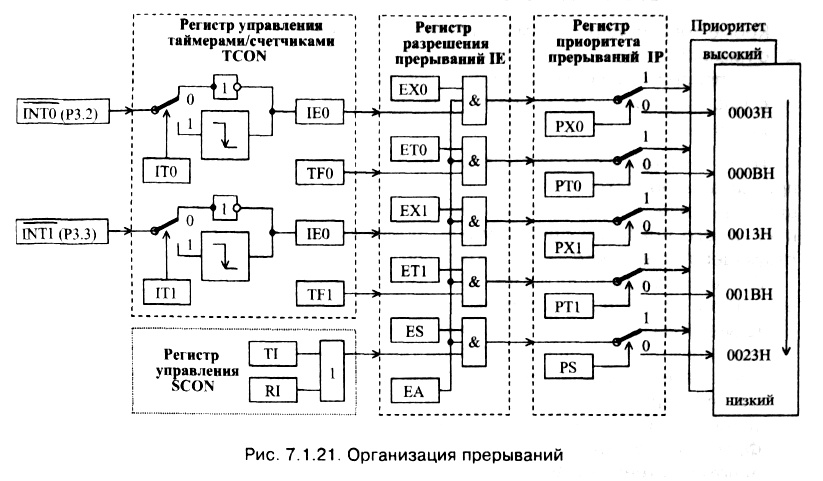

Организация прерываний.Средства прерывания МК позволяют откликаться на сигналы ?IМTnвнешних запросов (здесь и далееn= 0, 1), сигналыTFnпереполнения таймеров–счетчиков T/Cn, сигналы завершения последовательного обмена ТI,RI.

Для пояснения принципов организации прерываний от отдельных источников воспользуемся рис.7.1.21.

При поступлении внешнего сигнала запроса ?INTnпроисходит установка флагаIEnрегистра управления ТСОN, вызывающая выполнение соответствующей подпрограммы обслуживания прерывания.

При поступлении внешнего сигнала запроса ?INTnпроисходит установка флагаIEnрегистра управления ТСОN, вызывающая выполнение соответствующей подпрограммы обслуживания прерывания.

При этом вид активизации прерывания определяется состоянием флаговIТnрегистра ТСОN: приIТn= 1 — по уровню, приIТn= 0 — по фронту (перепаду из 1 в 0) сигнала ?INTn.

Если прерывание активизируетсяпо уровню,то сигнал запроса ?INTn= 0 действует постоянно и снимается в конце обслуживающей подпрограммы, чтобы не вызвать повторного обслуживания.

Сигнал запроса ?INTnраспознается аппаратными средствами МК за один машинный цикл (12 периодов тактовой частоты), после чего устанавливается флаг прерыванияIEn.

Флаг IEn сбрасывается после снятия сигнала ?INTn.

Отметим, что флагIEnпри переходе к подпрограмме обработки прерывания автоматически сбрасывается, A затем вновь устанавливается, если на соответствующем выводе порта сигнал ?INTn= 0 сохраняется.

Поэтому программная установка флаговIEn= 1 вызовет прерывание и после перехода к подпрограмме флаг будет сброшенIEn= 0. В случае активизации прерыванияпо фронту дляраспознавания сигнала ?INTnтребуется не менее двух машинных циклов.

Установка флагаIEnпроисходит после того, как две последовательные проверки покажут ?INTn= 1 в одном цикле и ?INTn= 0 — в другом.

Сброс флагаIEnвыполняется аппаратно при обращении к подпрограмме обслуживания прерывания.

Флаги запросов прерыванияTFnот таймеров–счетчиков Т/Cnустанавливаются после их переполнения и сбрасываются автоматически при передаче управления подпрограмме обслуживания.

Прерывание от последовательного порта вызывается аппаратной установкой флага прерывания передатчикаTIили флага прерывания приемникаRIв регистреSCONпо завершении передачи или приема байта данных.

Сброс флаговTI,RIпроизводится программным способом. Отметим, что флагиIEn,TFn,RI,TIмогут быть программно установлены или сброшены как соответствующие биты регистровTCON,SCON.

Кроме того, прерывания по ?INTnмогут вызываться программной установкой нулевого сигнала на выводах Р3.2, Р3.3 порта Р3.

Каждый из источников прерыванийIE0,TF0,IE1,TF1,RI?TIможет быть индивидуально разрешен или запрещен установкой или сбросом соответствующего бита в регистре разрешения прерыванияIE (рис.7.1.21).

РегистрIEсодержит также бит ЕА, значение которого ЕА = 0 запрещает сразу все прерывания.

При ЕА = 1 запрет на все прерывания снимается.

Уровни прерываний.

Структура приоритетов прерываний является двухступенчатой.

Каждому из пяти источников прерыванийIE0, ТР0,IE1,TF1,RI?TIможет быть индивидуально присвоен высокий (1) или низкий (0) уровень прерывания с помощью установки или сброса соответственно битов РХ0,PN0, РХ1, РТ1,PSв регистре приоритетов прерыванийIP (рис.7.1.21).

При этом, если одновременно приняты два запроса:

? сразными уровнями прерывания,то сначала обслуживается запрос с высоким уровнем приоритета;

? содинаковым уровнем приоритета,то их обработка будет производиться в следующей последовательности:IE0,TF0,IE1,TF1,RI?TI (стрелка на рис.7.1.21).

Кроме того, подпрограмма обработки прерывания:

? снизким уровнемможет быть прервана запросом прерывания с высоким уровнем приоритета, но не может быть прервана другим запросом с низким уровнем;

? свысоким уровнемне может быть прервана никаким другим запросом прерывания.

Последовательность обработки прерываний.

Установка флагов прерывания происходит в фазеS5P6машинного цикла.

В следующем машинном цикле выполняется опрос флагов внутренними средствами.

И после выполнения последнего цикла текущей команды производится аппаратный вызов соответствующей подпрограммы обслуживания, эквивалентный командеLCALL.

Обращение к подпрограмме обслуживания задерживается в трех случаях:

? при обработке подпрограммы прерывания с таким или высшим приоритетом; ?текущий машинный цикл не является последним циклом выполняемой команды;

? выполняется командаRETI(конец прерывания) или любая команда обращения к регистрамIE,IP.В этом случае перед вызовом подпрограммы обслуживания прерывания после окончания одной из вышеуказанных команд обязательно должна выполниться минимум еще одна команда текущей программы.

Флаг прерывания, установленный во время действия блокировки прерывания по одному из трех указанных выше условий и сброшенный до их снятия, не вызовет обслуживания соответствующего запроса прерывания.

Аппаратная командаLCALLзагружает в стек только содержимое счетчика командPC(в ячейку стека с младшим адресом — разряды 0–7, A в следующую ячейку — разряды 8–15), после чего записывает вPCстартовый адрес соответствующей подпрограммы обработки прерывания(03hдля источника прерыванияIE0, 0BhдляTF0, 13hдляIE1, BhдляTF1,23hдляRI?TI).По этому адресу может располагаться команда безусловной передачи управления(JMP)к первой ячейке памяти подпрограммы.

При необходимости в подпрограмму могут быть включены команды записи в стек(PUSH)содержимого регистров слова состояния программыPSW,аккумулятора A, указателя данныхDPTRи др.

В этом случае подпрограмма должна заканчиваться командами(POP)восстановления регистров из стека.

Подпрограмма обслуживания прерывания продолжается до выполнения команды RETI или RET .Команда RETI загружает в счетчик командPCдва байта адреса возврата из двух верхних ячеек стека и снимает запрет на все прерывания с уровнем приоритета, равным уровню приоритета обслуживаемого прерывания, т.е. восстанавливает логику прерывания.

При использовании команды RET восстанавливается только состояние счетчика команд, т.е. происходит возврат в прерванную программу.

Состояние логики прерывания команда RETне меняет, т.е. логика управления обслуживанием прерываний по–прежнему считает, что продолжает обслуживаться прерывание, подпрограмма обработки которого была закончена командой RET.Поэтому необходимо иметь программный механизм окончания процедуры обслуживания данного прерывания (восстановления логики управления обслуживания).

onetwoclick.ru

onetwoclick.ru