- Состав контроллера

- Процессор

- Блок управления программой

- Память программы

- Счетчик команд PC

- Стек

- Регистровая память

- Специальные регистры

- Регистры общего назначения

- Блок ввода/вывода

- Рассмотрим работу схемы

- Блок таймеров

- Сторожевой таймер

- Реализация сброса

- Сброс по включению питания

- Внешний сброс

- Специальные функции

- Защита программного кода от считывания

- Индивидуальная метка

Состав контроллера

Состав контроллера

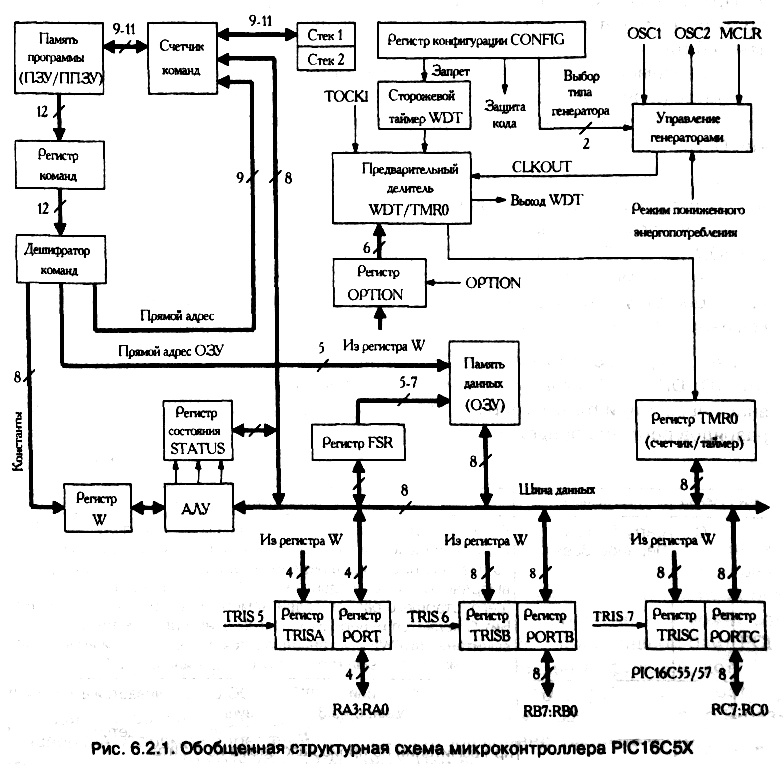

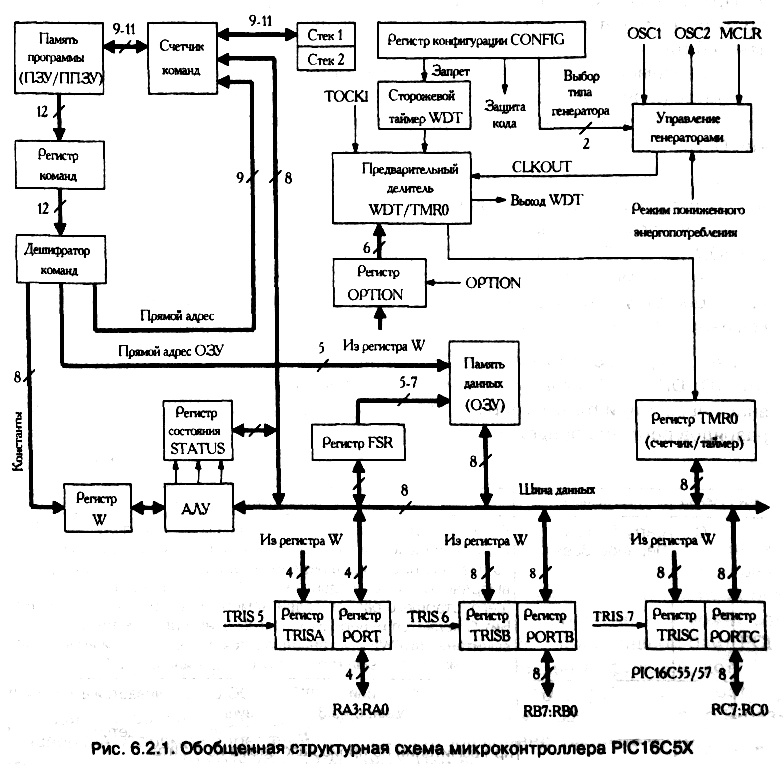

Обобщенная структурная схема микроконтроллеров (МК) семейства PIC16C5Xизображена на рис. 6.2.1. С функциональной точки зрения в контроллере можно выделить:

? процессор, к которому относятся арифметическо–логическое устройство (АЛУ), рабочий регистр W и регистр состояния STATUS

? блок управления программой содержащий память программы, регистр команд, дешифратор, счетчик команд и двухуровневый стек;

? регистровую память, состоящую из ОЗУ и специальных регистров;

? блок таймеров, включающий 8–разрядный счетчик/таймер (регистр TMR0), сторожевой таймер (WDT), предварительный делитель WDT/TMR0, регистр OPTION управления таймером TMR 0 и предварительным делителем;

? блок синхронизации и специальных функций, включающий модуль управления (узел выбора типа генератора, узел сброса и др.) и регистр конфигурации CONFIG;

? шинный интерфейс, предназначенный для передачи данных (8 бит), команд (12 бит), адресного кода (9–11 бит в зависимости от модели контроллера) и управляющих сигналов. Шина данных соединяет группу регистров ОЗУ, порты ввода/вывода и 8–разрядное АЛУ.

Назначение внешних выводов микроконтроллера приведено в табл. 6.2.1.

Назначение внешних выводов микроконтроллера приведено в табл. 6.2.1.

Рассмотрим назначение отдельных блоков контроллеров и выполняемые ими функции.

Процессор

Основными функциями процессора являются обработка данных и выдача сведений о своем состоянии.

Арифметическо–логическое устройство (АЛУ)предназначено для обработки данных, которая осуществляется с помощью арифметических, логических и битовых операций, предусмотренных системой команд для рассматриваемого семейства.

При выполнении арифметических (сложение, вычитание) и логических (И, ИЛИ, исключающее ИЛИ) команд с двумя 8–разрядными операндами один из них поступает в АЛУ из рабочего регистра W, другой — из любого регистра общего назначения (POH) или регистра специальных функций. Результат операции может быть размещен в одном из регистров–источников.

При выполнении команд с одним операндом (инкремент, декремент, сдвиги вправо и влево) источником операнда может быть любой из указанных выше регистров, результат операции размещается в регистре–источнике или в рабочем регистре W (даже, если он не является источником).

При выполнении битовых команд происходит сброс/установка бита в адресуемом регистре, выполнение/пропуск следующей команды в зависимости от значения бита.

В зависимости от результата выполненной операции могут измениться значения битов переноса С, дополнительного (десятичного) переноса DCи нуля Z в регистре состояния STATUS . Битовые команды не изменяют значений битов состояния С, DC, Z.

Рабочий регистр W выполняет функции аккумулятора: может быть источником и приемником 8–разрядных операндов для АЛУ, поддерживает передачу данных в регистры управления портами RIS и в регистр управления таймером

OPTION (рис. 6.2.1) с помощью специальных команд. В отличие от аккумулятора регистр W не может быть прямо адресован, т. е. в адресном пространстве данных его адрес отсутствует. Для его загрузки и пересылки используются специальные команды (MOVW f, MOVLW k).

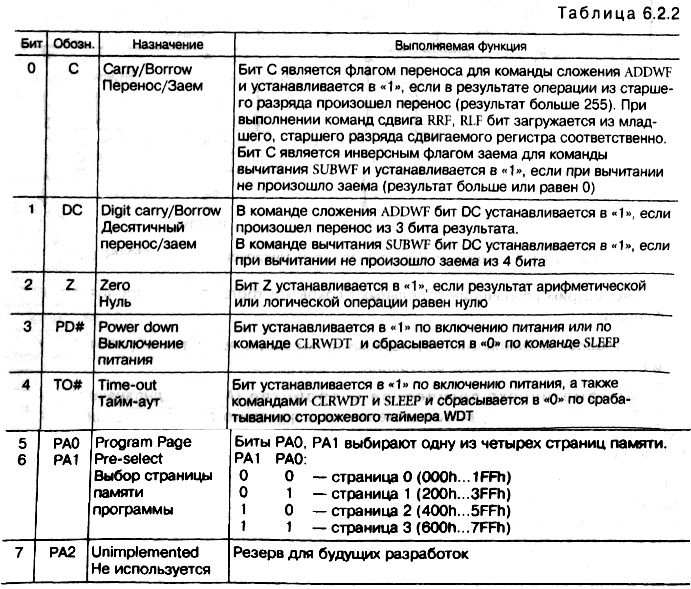

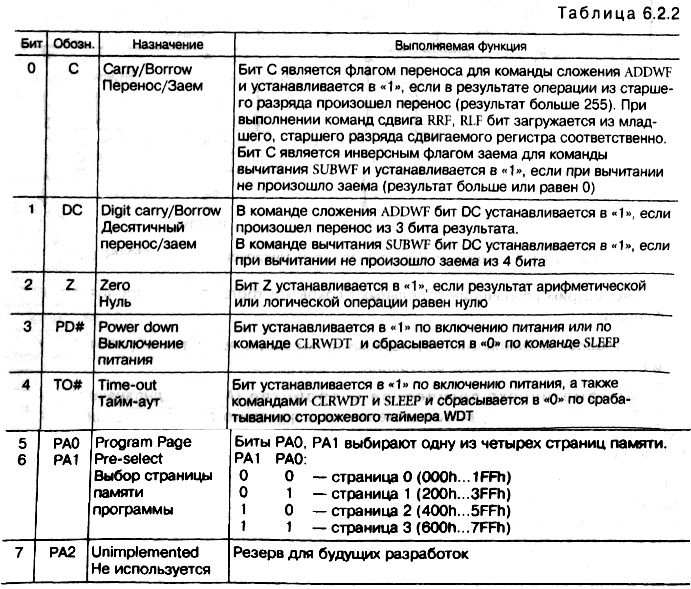

Регистр состояния

STATUS предназначен для хранения флагов состояния АЛУ (С, DC, Z), флагов состояния контроллера при сбросе (PD#, ТО#, где # — знак инверсии) и биты выбора страниц памяти программы (РА0, РА1). Назначение разрядов регистра приведено в табл. 6.2.2.

Регистр STATUS доступен для любой команды. Однако следует иметь в виду, что при выполнении команд с использованием регистра состояния биты PD# и ТО# устанавливаются аппаратно и не могут быть изменены программно. Например, при выполнении команды CLRF сброса регистра STATUS сначала обнуляются все биты, кроме битов PD# и ТО#, а затем для фиксации нулевого результата устанавливается бит Z= 1. После этой команды регистр STATUS

переходит в состояние 000 bТО bРО 100, где биты bТО, bРО остались без изменения. Некоторые команды могут изменять значение бит. Поэтому для целенаправленного изменения значений бит регистра состояния рекомендуется использовать только те команды, которые не вызывают случайного изменения бит PD# и ТО#. К ним относятся команды битовой установки BCF, BSF, а также пересылки MOVWF и обмена тетрад SWAPF.

Блок управления программой

Этот блок является основным средством, обеспечивающим выполнение программы.

Память программы

В этой памяти хранится код программы. Память программы контроллеров семейства PIC16C5X содержит 512, 1024 или 2048 ячеек, в каждой из которых может храниться 12–битная инструкция. Для доступа к ячейкам памяти в зависимости от их количества используется 9–, 10– или 11–разрядный адресный код. Память разбита на страницы по 512 слов (ячеек), выборка которых осуществляется путем изменения значений разрядов 10, 11 кода с помощью бит РА0, РА1 регистра состояния STATUS.

Счетчик команд PC

В счетчике команд формируется адресный код требуемой разрядности для очередной команды. Для каждой модели контроллера разрядность счетчика команд PC определяется объемом резидентного постоянного запоминающего устройства, которое хранит прикладную программу, и может составлять 9, 10 или 11 бит. Разряды 0…7 адресного кода, или младший байт PCL, счетчика команд интерпретируются как регистр специальных функций, который имеет собственный адрес в адресном пространстве памяти данных и поэтому программно доступен. Разряд 8 кода (вместе с байтом PCL) поступает по 9–разрядной шине прямой адресации из дешифратора команд, разряды 9, 10 — из регистра состояния STATUS (биты РА0, РА1). При выполнении программы содержимое счетчика автоматически увеличивается, также автоматически осуществляется переход на следующую страницу памяти.

Если счетчик команд PC загружается какой–либо командой (например MOVWF PC, ADDWF PC или BSF РС,5), изменяющей его содержимое, то в младший байт PCL счетчика команд записывается результат операции в 8–разрядном формате; бит 8 сбрасывается в 0, а биты 9, 10 загружаются из регистра состояния STATUS.

Наличие 0 в разряде 8 свидетельствует о том, что доступны только первые 256 адресов каждой страницы памяти программ. Такое действие оказывает команда CALL k (k= 0–255) вызова подпрограммы. Команда передачи управления GOTO k (k= 0–511), поступающая по 9–разрядной шине, обеспечивает прямой доступ к памяти программ по всем адресам текущей страницы.

Стек

Двухуровневый аппаратный стек предназначен для хранения только содержимого счетчика команд и используется при выполнении команды CALL вызова подпрограммы. Его разрядность соответствует разрядности адресного кода.

При вызове подпрограммы осуществляется переход на новый адрес. Для продолжения основной программы адрес ее следующей команды помещается в стек на временное хранение. При этом содержимое счетчика команд увеличивается на единицу и загружается в стек 1, предыдущее содержимое стека 1 переносится в стек 2, а предыдущее содержимое стека 2 теряется. Таким образом, глубина вложения подпрограмм равна 2.

После выполнения подпрограммы адрес следующей команды основной программы возвращается в счетчик команд. Так как стек содержит полный адрес возврата, то подпрограмму можно вызвать из любого места в программе.

Регистр команд служит для хранения текущей команды в процессе ее исполнения.

Дешифратор команд обеспечивает прямую адресацию памяти программы и данных, а также выборку константы из кода команды (при непосредственной адресации).

Регистровая память

Регистры микроконтроллера разделяются на две группы (рис. 6.2.2).

Специальные регистры

Эти регистры управляют работой отдельных узлов контроллера, конфигурацией портов ввода/вывода, адресацией памяти, режимами таймеров. По выполняемым функциям можно выделить две разновидности регистров:

? регистры, относящиеся к базовым функциям: рабочий регистр W, программный счетчик PC, регистр состояния OPTION, регистр косвенной адресации FSR, регистр таймера (TMR0);

? регистры, относящиеся к периферийным устройствам: регистры ввода/вывода PORTA, PORTB, PORTC, регистры управления порами TRISA, TRISB, TRISC.

Специальные регистры (кроме FSR) рассмотрены при описании соответствующих узлов контроллера. Регистр косвенной адресации FSR совместно с псевдорегистром INDF (реально не существует) предназначен для косвенной адресации памяти данных. В ранних моделях контроллеров его разрядность составляет пять бит, в поздних — семь бит. Если в программе не используется режим косвенной адресации, регистр FSR может быть задействован как 5(7)–битный регистр общего назначения. Принципы адресации изложены ниже.

Регистры общего назначения

Регистры этой группы используются программой для хранения переменных по усмотрению пользователя и образуют память данных контроллера.

С точки зрения доступа к регистровой памяти можно выделить пять групп по 16 регистров в каждой группе (рис. 6.2.2). Две группы из специальных регистров и регистров общего назначения (POH) объединены в банк 0, каждая из оставшихся трех групп представляет собой банк POH.

В ранних моделях МК семейства PIC16CX использовалась только прямая адресация к регистрам, обеспечивающая по пятиразрядной адресной шине доступ к 32 регистрам банка 0. Емкость памяти данных составляла 24–25 байт (16 + 8–9 POH). В поздних моделях максимальную емкость памяти данных составляет 72–73 байта (24–25 + 16×3 POH). Использование прямой и косвенной адресации обеспечивает доступ ко всем регистрам.

Блок ввода/вывода

Для ввода/вывода информации используется три набора из регистров двух видов:

?регистры ввода/вывода портов А, В, С, причем регистры портов В и С имеют 8 разрядов, а регистр порта А — 4 разряда (отсутствующие 4 старших разряда считываются как нули);

? регистры TRIS управления портами, задающие направление передачи данных через порты. Регистры доступны только для записи. В них с помощью команды TRIS заносится содержимое рабочего регистра W.

Если значение в i–м разряде регистра TRIS равно 0, то внешний i–й вывод порта выполняет функции выхода и обеспечивает выдачу бита данных во внешнее устройство. Значение 1 в разряде определяет соответствующий вывод порта как вход. Все разряды портов могут быть запрограммированы индивидуально;

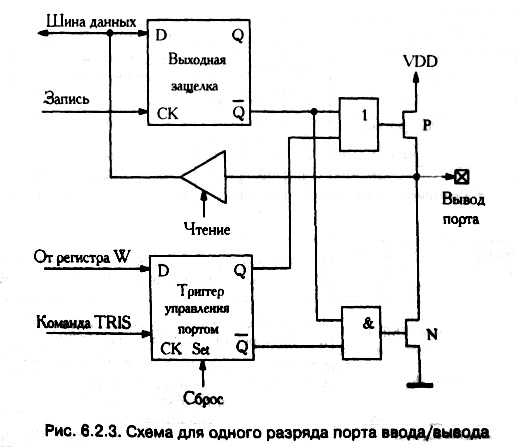

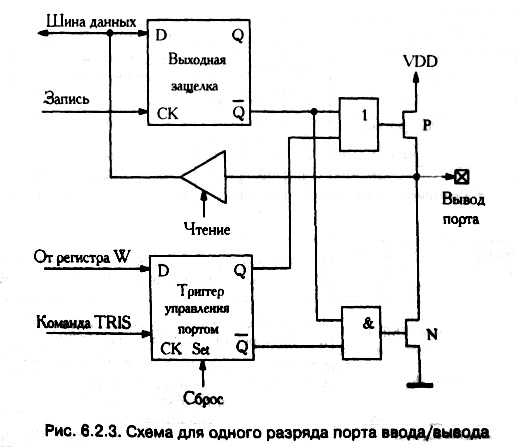

? логическая схема одного разряда порта ввода/вывода изображена на рис. 6.2.3. В ее состав входят: два D

–триггера, управляемый буфер, логические элементы И и ИЛИ, двухтактный усилитель на КМОП транзисторах. Выходы портов представляют собой защелки. Их состояние не меняется до следующей записи в порт. Для установки режима ввода/вывода используется триггер регистра TRIS управления портом.

Рассмотрим работу схемы

? в режиме ввода, когда на выходах триггера управления портом установлены сигналы Q= 1, ¯Q=0, оба транзистора двухтактного выходного каскада закрыты (отключены): транзистор Р единичным сигналом на затворе, транзистор N — нулевым. Сигналом «Чтение» = 1 входной буфер открыт, и бит данных с вывода порта поступает линию шины данных. Ввод данных в порт не стробируется. Чтение порта производится соответствующими командами (например MOVF PORTB, W), во время выполнения которых уровень на входах порта остается постоянным;

? в режиме вывода, когда на выходах триггера регистров управления TRISA, TRISB или TRISC установлены сигналы Q = 0, ¯Q = 1, состояние логических элементов зависит от содержимого выходной защелки, в которую записывается выводимый бит данных. При выводе единичного бита с выхода защелки снимается сигнал ¯Q = 0, поэтому логические элементы открывают транзистор Р и закрывают транзистор N. На выводе порта устанавливается единичный уровень. При выводе нулевого бита с выхода защелки снимается сигнал ¯Q = 1, поэтому логические элементы открывают транзистор N и закрывают транзистор Р. На выводе порта устанавливается нулевой уровень. Состояние защелки не меняется до следующей записи в порт.

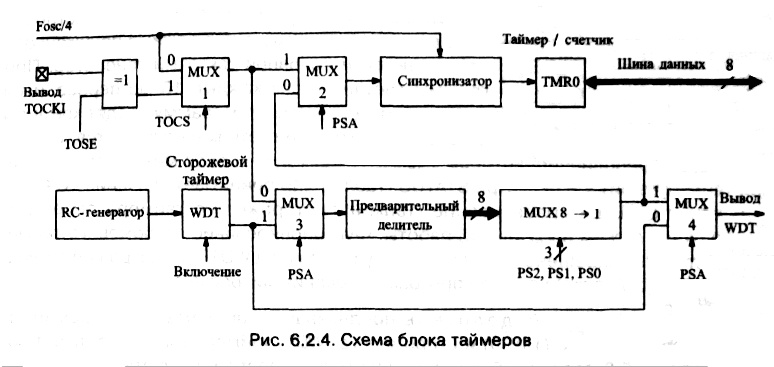

Блок таймеров

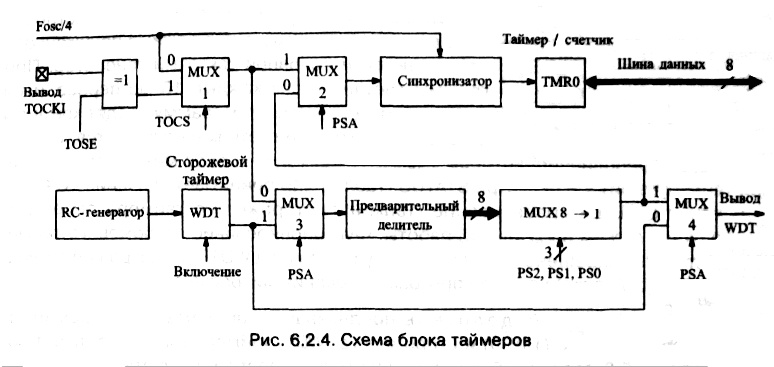

В состав этого блока (рис. 6.2.4) входят:

? 8–разрядный таймер–счетчик (регистр TMR0);

? сторожевой таймер (WDT);

? предварительный делитель частоты для TMR0/WDT;

? мультиплексоры для управления режимами с помощью бит регистра OPTION.

Регистр OPTION доступен только для записи. С помощью команды OPTION данные из рабочего регистра W переписываются в регистр OPTION. Назначение бит регистра приведено в табл. 6.2.3.

Для описания структурно–функциональной организации блока таймеров воспользуемся упрощенной структурной схемой, изображенной на рис. 6.2.4.

Таймер–счетчик содержит:

? логический элемент исключающее ИЛИ и мультиплексоры MUX–1, MUX–2, позволяющие с помощью бит TOSE, TOCS, PSA регистра OPTION задать режим работы таймера/счетчика согласно табл. 6.2.3;

? синхронизатор, обеспечивающий внутреннее тактирование с задержкой на два командных цикла;

? непосредственно 8–разрядный регистр–счетчик TMR0, доступный по чтению и записи.

Возможны два режима работы таймера–счетчика:

? режим таймера, для которого характерно увеличение содержимого TMR0 в каждом командном цикле при отсутствии предварительного делителя. Режим выбирается установкой в «0» бита TOCS (разряд 5 регистра OPTION).

При записи в TMR0 увеличение счетчика задерживается на два последующих цикла выполнения команды. Для проверки регистра TMR0 на нуль без влияния на процесс счета можно пользоваться командой MOVF TMR0, W;

? режим счетчика, для которого содержимое TMR0 увеличивается по каждому перепаду 1 —> 0 или 0 —> 1 на внешнем выводе TOCKI.

Вид перепада задается битом выбора фронта переключения TOSE (разряд 4 регистра OPTION).

Режим выбирается установкой в 1 бита TOGS (разряд 5 регистра OPTION).

Сторожевой таймер

Основное назначение сторожевого таймера WDT (WatchDog Timer) — защита микроконтроллера от сбоев:

? при нормальном порядке исполнения программы сторожевой таймер WDT периодически переходит в начальное состояние через заданное время выдержки;

? при нарушении порядка исполнения программы (при сбое) сторожевой таймер не переходит в начальное состояние, происходит его переполнение, которое вызывает сброс микроконтроллера.

Номинальное время выдержки сторожевого таймера, называемое периодом тайм–аута WDT, выбирается исходя из заданных интервалов изменения питающих напряжений, температуры, технологического разброса параметров и других дестабилизирующих факторов. В контроллерах PIC16C5X период тайм–аута составляет 18 мс. Для его увеличения (до 2,3 секунды) можно использовать встроенный предварительный делитель с программируемым коэффициентом деления частоты (до 128 раз).

Внешний тактовый генератор может быть построен:

? по описанной выше трехточечной схеме с емкостной обратной связью (рис. 6.2.5, б);

? по схеме с включением кварцевого (керамического) резонатора в цепь обратной связи на частоте последовательного резонанса (рис. 6.2.5, в). При установке бит FOSC1 =FOSC0= 1 регистра конфигурации в микроконтроллерах предусмотрены внутренние средства (триггер Шмитта и КМОП транзистор) для построения RC–генератора (рис. 6.2.5, г) с использованием всего лишь двух внешних элементов, задающих частоту внутреннего тактового сигнала. Когда не предъявляются высокие требования к точности и стабильности частоты генератора, использование RC–генератора позволяет дополнительно уменьшить стоимость приложения.

На выводе OSC2/CLKOUT в режиме RC присутствует сигнал с частотой генератора, деленной на четыре, который может быть использован для синхронизации других схем.

Реализация сброса

Микроконтроллеры имеют специальную схему, позволяющую выполнить следующие виды сброса:

? сброс по включению питания (POR);

? сброс по внешнему входу MCLR# при обычной работе и в режиме пониженного энергопотребления SLEEP, где # — знак инверсии;

? сброс по сторожевому таймеру WDT.

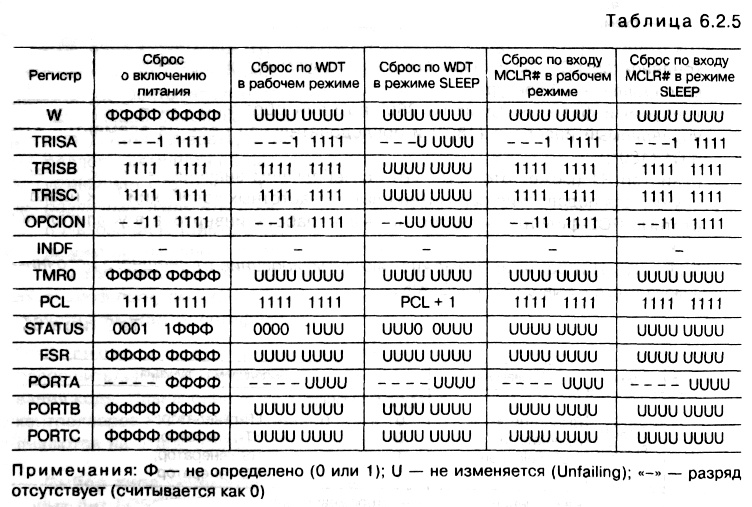

Состояние регистров после сброса приведено в табл. 6.2.5.

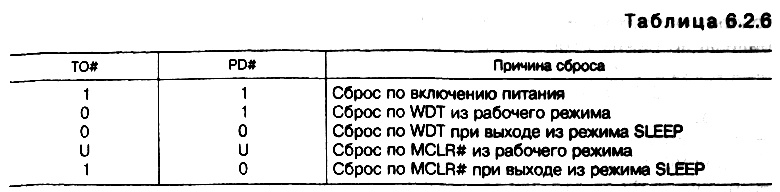

Некоторые регистры всегда устанавливаются в определенное состояние, другие регистры при сбросе по включению питания имеют неопределенное значение, в остальных случаях их состояние не изменяется (U). Биты тайм–аута ТО# и выключения питания Р D #регистра состояния (табл. 6.2.2) устанавливаются в определенное состояние в зависимости от причины сброса (табл. 6.2.6).

В состав схемы сброса входят (рис. 6.2.6):

? схема включения и триггер Шмитта, формирующие импульсы для запуска RS–триггера и четкой фиксации момента его установки;

? таймер сброса DRT и внутренний RC–генератор, используемые для формирования сигнала выдержки времени (номинальное значение 18 мс) состояния сброса микроконтроллера. Таймер DRT запускается после перехода в высокий уровень сигнала на выводе MCLR#;

? RS–триггер и логические элементы. В исходном состоянии снимаемый с инверсного выхода RS–триггера сигнал сброса микроконтроллера Q# =1. При появлении единичного логического уровня на одном из входов элемента ИЛИ триггер переводится в состояние сброса (Q# = 0).

Длительность сигнала Сброс составляет 18 мс. С помощью таймера сброса DRT триггер переводится в исходное состояние, при котором сигнал Сброс Q# =1.

Сброс по включению питания

Для реализации этого сброса необходимо соединить внешние выводы MCLR# и VDD.При появлении на этих выводах напряжения происходит установка RS–триггера и запуск таймера сброса DRT.

На выходе триггера формируется сигнал Сброс Q# = 0. Через 18 мс таймер ORT сбрасывает триггер, и тем самым прекращает действие сигала Сброс. Запуск контроллера завершается и он готов к работе. При этом все параметры (напряжение питания, частота, температура и др.) должны соответствовать допустимым.

Внешний сброс

Когда напряжение питания устанавливается очень медленно и после окончания выдержки времени таймера D RT напряжение питания не достигло номинального значения микроконтроллер может не запустится или запуститься некорректно. Кроме того, схема сброса может также не обеспечить достаточную выдержку времени в устройствах с низкочастотными кварцевыми генераторами, которые требуют достаточно большего времени для запуска и стабилизации режима генерации. В этих случаях необходимо использовать внешнюю схему сброса микроконтроллера.

На рис. 6.2.7, а приведена широко распространенная схема внешнего сброса, в которой:

? элементы R и С определяют скорость нарастания напряжения;

? диод VD предназначен для разряда конденсатора С при выключении питания;

? резистор R 3 служит для ограничения тока по выводу MCLR

# при перезарядке конденсатора С и импульсных помехах (выполняет защитные функции).

На рис. 6.2.7, б приведена схема внешнего сброса с использованием стабилитрона Эта схема вырабатывает сигнал сброса при понижении напряжения. Когда напряжение питания VDD становится ниже, чем напряжение UCT + 0,7 В, где 0,7 В — напряжение отпирания транзистора, UCT — напряжение на стабилитроне, транзистор запирается. напряжение на входе MCLR# становится равным нулю, срабатывает R 3–триггер и контроллер переводится в состояние сброса.

На рис. 6.2.7, в приведен вариант схемы сброса с резистивным делителем напряжения.

Специальные функции

Режим пониженного энергопотребления (SLEEP).

Вход в режим инициируется командой SLEEP, после выполнения которой:

? сбрасывается и начинает новый отсчет времени сторожевой таймер WDT, если он разрешен, т. е. бит 2 в регистре конфигурации WDTE = 1 (табл. 6.2.4);

? сбрасывается бит выключения питания (PD# = 0) и устанавливается бит тайм–аута (ТО# = 1) в регистре состояния STATUS(табл. 6.2.2);

? выключается тактовый генератор;

? порты ввода/вывода сохраняют состояние, которое они имели до входа в режим SLEEP.

Выход из режима SLEEP возможен в следующих случаях:

? по внешнему сбросу подачей сигнала с нулевым логическим уровнем на вывод MCLR#;

? по сбросу при срабатывании сторожевого таймера WDT.

В обоих случаях происходит сброс микроконтроллера. Биты ТО# и PD# регистра состояния определяют причину сброса (табл. 6.2.2). При выходе из режима пониженного энергопотребления SLEEP сторожевой таймер WDT переводится в нулевое состояние независимо от причины сброса.

Для минимизации потребления в режиме SLEEP принимаются специальные меры, например, все разряды внешних портов должны находиться либо на уровне общего вывода VSS, либо на уровне напряжения питания VDD.

Защита программного кода от считывания

Для защиты кода, записанного в память программ (ППЗУ или ПЗУ), следует установить в нуль все имеющиеся биты защиты CP регистра конфигурации CONFIG (табл. 6.2.4). После выполнения этой операции:

? содержимое памяти программы не считывается в исходном виде, тем самым невозможно реконструировать записанную программу. Чтение любого адреса памяти программы дает кодированный результат в виде двоичного кода 00000000ФФФФ, где Ф = 0 или 1;

? невозможно допрограммировать контроллер. Однако для микроконтроллеров с ППЗУ возможно допрограммирование адресов 00h–3Fh. Кодирование осуществляется побитовым выполнением операции «Исключающее ИЛИ» между старшей и средней тетрадами содержимого памяти программы, а затем с младшей тетрадой. Результирующее 4–битовое значение используется для контроля правильности программирования. Программа, записанная по этим адресам, не может считаться защищенной от считывания. Для контроля правильности записи при допрограммировании области памяти 00h–3Fh необходимо учитывать метод кодирования, используемый для защиты памяти программы;

? сохраняется возможность считывания и модификации содержимого регистра конфигурации CONFIG.

Индивидуальная метка

В микроконтроллеры PIC16C5X имеются четыре специальных адреса, не являющиеся частью памяти программы. По этим адресам хранится идентификационный код пользователя, контрольная сумма или другие данные. Как и слово конфигурации, они могут быть прочитаны или записаны только с помощью программатора. Программно эти адреса недоступны.

onetwoclick.ru

onetwoclick.ru

Спасибо автору многое оказалось полезным!