Общие сведения.

Общие сведения.

Цифровые сигнальные процессоры (Digital Signal Processors — DSP) представляют собой самостоятельный класс специализированных процессоров с RISC–архитектурой, предназначенных для решения задач цифровой обработки сигналов, к которым относятся распознавание звука и речи, цифровая звукотехника, обработка изображений, цифровая фильтрация, спектральный анализ и др.

Цифровая обработка сигналов требует большого объема вычислений, выполняемых, как правило, в реальном времени. Основными отличительными особенностями DSP от обычных микропроцессоров являются:

? использование гарвардской архитектуры, при которой для хранения программ и данных используются раздельные запоминающие устройства, A также раздельные шины данных и адреса, что позволяет совмещать выборку и исполнение команд;

? применение двух– или трехкаскадного конвейера, позволяющего одновременно обработать две или три команды и сократить длительность командного цикла;

? применение аппаратного умножителя, который выполняет наиболее распространенную операцию умножения двух чисел за один командный цикл. В обычных процессорах эта операция занимает много времени, так как реализуется за несколько тактов сдвига и сложения;

? наличие специальных команд для цифровой обработки сигналов: умножение с накоплением и адресация к кольцевым буферам (для цифровой фильтрации); изменение порядка бит адреса на обратный (для быстрого преобразования Фурье); битовые операции (для графики) и др. В этом разделе рассмотрено семейство процессоров ADSP–21XX фирмы Analog Devices, которые относятся к классу процессоров с фиксированной точкой и являются наиболее оптимальными по соотношению цена/качество. Кроме того, для семейства ADSP–21XX имеется полный набор программных и аппаратных средств поддержки разработчика, включающий в себя:

? построитель систем для определения архитектуры проектируемой цифровой системы (размера внешней RAM/ROM памяти, расположения памяти данных и команд, отображение портов ввода/вывода);

? ассемблер, поддерживающий высокоуровневый набор команд и модульное программирование;

? линкер (компоновщик), позволяющий оптимально расположить данные и команды по аппаратным узлам проектируемой системы;

? эмулятор для проведения интерактивной покомандной эмуляции аппаратной конфигурации, описанной в построителе систем;

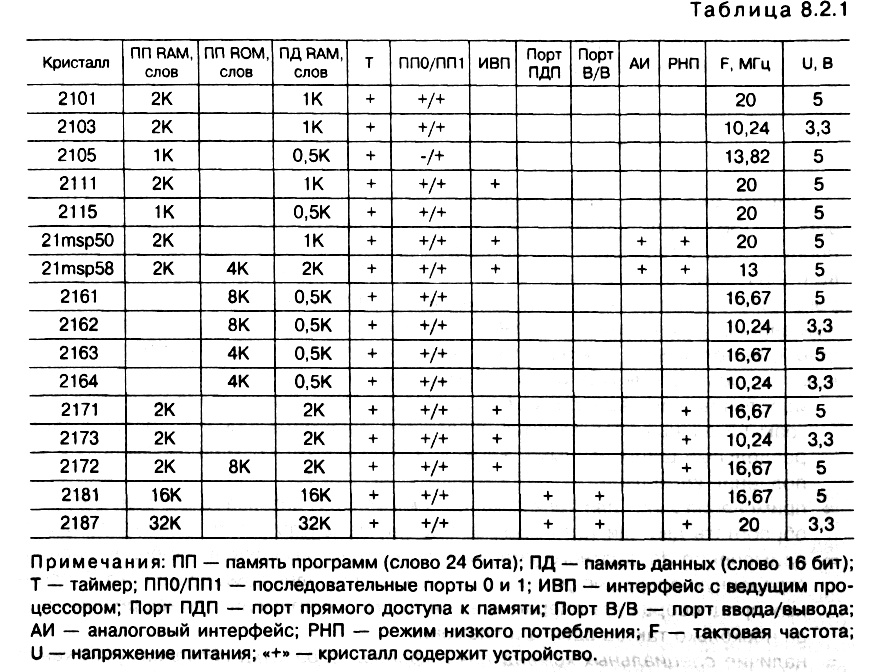

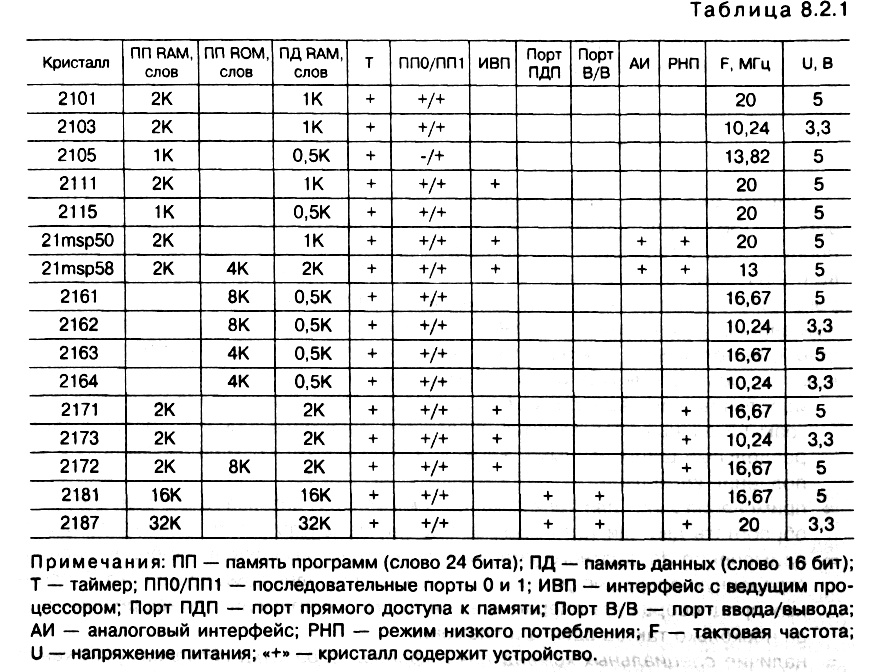

? программатор ППЗУ для чтения вывода линкера и формирования файлов, совместимых с программаторами. Общая характеристика семейства ADSP–21XX. Семейство ADSP–21XX включает в себя набор однокристальных процессоров с общей базовой архитектурой, оптимизированной для цифровой обработки сигналов и других приложений, требующих быстрых вычислений. В табл. 8.2.1 приведен ряд показателей для микросхем процессоров ADSP–21XX.

- Процессоры семейства ADSP–21ХХ позволяют

- Состав ADSP

- Вычислительный блок

- Блок внутренней памяти

- Таймер

- Блок последовательного интерфейса

- Устройство обмена между шинами

- Блок интерфейса с ведущим процессором

- Блок аналогового интерфейса

- Шины процессора

- Системный интерфейс

- Синхронизация процессора

- Сброс

- Программная начальная загрузка

- Внешние прерывания

- Выводы флагов

- Интерфейс с загрузочной памятью

- Интерфейс с памятью программ

- Интерфейс с памятью данных

Процессоры семейства ADSP–21ХХ позволяют

? в течение одного процессорного цикла выполнить стандартные арифметические и логические операции, операции умножения и умножения с накоплением, арифметические и логические сдвиги и другие операции;

? вести обработку данных с повышенной точностью. В частности использование 40–битного регистра–аккумулятора дает возможность накапливать расширенные суммы произведений, достаточно часто встречающиеся при цифровой обработке сигналов, что обеспечивает 8–битную защиту от потери данных при переполнениях. При последовательном выполнении операций умножения со сложением должно произойти 255 переполнений регистра–аккумулятора и только 256–е переполнение приведет к потере данных;

? аппаратно (с помощью генератора адресов данных) реализовать кольцевые буферы и обеспечить доступ к ним, что весьма важно для таких приложений, как цифровые фильтры;

? организовать (с помощью генератора адресов команд) циклы и переходы, широко используемые при цифровой обработке сигналов, без дополнительных процессорных циклов ожидания;

? обеспечить ряд других операций для цифровой обработки сигналов (обратный порядок расположения бит при адресации, примитивы операций деления и арифметики с плавающей точкой и др.). Высокая производительность процессоров достигается благодаря их способности параллельного выполнения большого числа микроопераций. В течение одного цикла процессор способен:

? сформировать адрес следующей команды;

? загрузить из памяти следующую команду;

? загрузить два операнда из внутренней и/или внешней памяти;

? обновить два указателя на данные;

? выполнить вычислительную операцию;

? принять и/или передать данные через последовательный порт, через интерфейс с ведущим процессором (при наличии) и аналоговый интерфейс (при наличии).

Состав ADSP

Для выявления особенностей структурно–функциональной организации процессоров семейства ADSP–21ХХ воспользуемся обобщенной схемой, представленной на рис. 8.2.1. В процессоре можно выделить следующие основные блоки:

? вычислительный блок;

? блок генераторов адресов;

? блок внутренней памяти;

? таймер;

? блок последовательного интерфейса;

? устройство обмена между шинами данных;

? блок интерфейса с ведущим процессором;

? блок аналогового интерфейса. Связь между блоками осуществляется по внутренним шинам процессора, связь процессора с периферийными устройствами — по внешним шинам. Рассмотрим назначение и состав отдельных блоков обобщенной схемной модели процессора.

Вычислительный блок

Этот блок содержится в каждом процессоре. В его состав входят три независимых полнофункциональных устройства:

? арифметическо–логическое устройство (Arithmetic/Logic Unit — ALU), выполняющее стандартный набор арифметических и логических операций, A также примитивы деления;

? умножитель–аккумулятор (Multiplier/Accumulator — MAC), или накопитель, обеспечивающий выполнение операции умножения двоичных чисел за один процессорный цикл, A также совмещенных операций сложения с умножением и вычитания с умножением;

? устройство сдвига (SHIFTER), предназначенное для выполнения логических и арифметических сдвигов, операций нормализации и денормализации чисел (операндов), экспоненциальных операций, A также операций над числами более одного слова с плавающей точкой. Вычислительный блок непосредственно обрабатывает 16–разрядные данные следующих типов:

? строки битов, представляющие собой двоичную запись чисел длиной 16 бит. Примером использования этого типа данных являются логические операции;

? знаковые числа, использующие для записи дополнительный код;

? числа без знака, принимающие только положительные значения и имеющие диапазон вдвое больший, чем знаковые. Примером беззнаковых чисел являются младшие слова чисел с двойной точностью;

? дробный формат 1.15, в котором левый крайний бит числа обозначает его знак, A остальные 15 бит — значение числа. Ниже приведены пределы изменения положительных и отрицательных чисел в дробном формате и их десятичные значения. Пределы чисел в формате 1.15 Пределы десятичных значений 0000 0000 0000 0001 …0l11 1111 1111 1111 0.000031.. .0.999969 или 0x0001…0x7FFF 1111 1111 1111 1111..1000 0000 0000 0000 –0.000031…–1.000000 или 0xFFFF…0x8000 Блок генераторов адресов. Этот блок имеется в каждом процессоре. В его состав входят:

? генератор адресов команд (Program Sequencer — PS), формирующий адреса команд для памяти программ;

? два генератора адресов данных DAG1, DAG2 (Data Address Generators — DAG), обеспечивающие адресацию при пересылке данных в вычислительное устройство. При этом DAG1 формирует адреса только для памяти данных, позволяя изменять порядок следования бит в адресе. Генератор DAG2 способен формировать адреса, как для памяти данных, так и для памяти программ. Оба генератора эффективно используются для адресации кольцевых буферов;

? генератор адреса загрузки, используемый для аппаратного формирования последовательности адресов при начальной загрузке внутренней RAM–памяти программ из внешней ROM–памяти.

Блок внутренней памяти

Этот блок содержат все процессоры, кроме ADSP–2100. В него входят расположенные на кристалле RAM–память данных и RAM–память (в некоторых сериях микросхем ROM–память) программ. Внутренняя память отображается на часть общего адресного пространства памяти данных и программ.

В микросхемах с RAM–памятью программ после включения питания необходимо выполнить начальную загрузку памяти из внешней загрузочной памяти.

За один цикл процессор способен считать два операнда из памяти данных и одну команду из памяти программ.

Таймер

Все процессоры семейства ADSP–21XX содержат программируемый таймер/счетчик с 8–битным масштабированием. После каждого процессорного цикла содержимое 16–разрядного регистра–счетчика декрементируется и по достижении нулевого значения таймер генерирует прерывание. Затем регистр–счетчик автоматически загружается из 16–разрядного регистра интервала и процесс повторяется.

Блок последовательного интерфейса

Этот блок имеется в каждом процессоре семейства ADSP–21XX и содержит два двунаправленных последовательных порта SPORT0, SPORT1 (за исключением ADSP–2105) с двойной буферизацией и устройство компрессии/декомпрессии данных. Порт SPORT0 способен работать в многоканальном режиме с организацией обмена по 24 или 32 управляемым (с возможностью блокировки) каналам. Порт SPORT1 допускает альтернативное использование четырех линий, которые помимо основного назначения могут быть сконфигурированы для приема внешних сигналов запроса прерываний ?IRQ0, ?IRQ1 и входного флага FI (Flag In) и выдачи выходного флага FO (Flag Out). Каждый порт может тактироваться от собственного таймера или от внешнего источника тактовой частоты. При передаче слов может быть использована кадровая синхронизация. С помощью устройства компрессии/декомпрессии могут быть реализованы алгоритмы сжатия/восстановления данных по А– и u–законам. Различные режимы работы последовательных портов подробно изложены ниже.

Устройство обмена между шинами

Это устройство позволяет произвести обмен данными между шиной данных памяти данных DMD и шиной данных памяти программ РМD.

Блок интерфейса с ведущим процессором

Этот блок имеется в процессорах ADSP–2111, ADSP–21msp50, ADSP–21msp58, ADSP–2171, ADSP–2172, ADSP–2173. Блок интерфейса позволяет организовать обмен информацией между ведомым (содержащим этот блок) и внешним ведущим процессорами. Интерфейс с ведущим процессором (Host Interface Processor — HIP) представляет собой параллельный порт ввода/вывода, к которому подсоединяется ведущий процессор.

В качестве ведущего процессора может быть использован как процессор семейства ADSP–21XX, так и другой, например, Intel 8051.

Интерфейс HIP состоит из блока управления и ряда регистров, имеет 16–разрядную шину для ввода/вывода данных и 11 управляющих выводов. Интерфейс может быть настроен на обмен 8– или 16–разрядными операндами;

на мультиплексированную шину адреса/данных или раздельные шины; на раздельные строб–импульсы для чтения/записи иди на строб–импульс чтения/записи и строб–импульс данных.

Блок аналогового интерфейса

Этот блок имеется только в процессорах ADSP–21msp50, ADSP–21msp58. Он обладает средствами для работы со смешенными аналого–цифровыми сигналами.

Шины процессора

В процессах семейства ADSP–21XX для связи между внутренними блоками используются пять шин (рис. 8.2.1):

? 14–разрядные шина адреса памяти данных (Data Memory Address — DMA) и шина адреса памяти программ (Program Memory Address — PMA), обеспечивающие доступ соответственно к 16–разрядным ячейкам памяти данных и 24–разрядным ячейкам памяти программ. Адрес памяти данных может быть задан непосредственно в команде (непосредственная адресация) или сформирован генератором адресов данных (косвенная адресация);

? 16–разрядная шина данных памяти данных (Data Memory Data — DMD) и 24–разрядная шина данных памяти программ (Program Memory Date — PMD), предназначенные для пересылки из памяти или в память соответственно данных и команд/данных;

? 16–разрядная шина результатов (Result — R), предназначенная для обмена результатами между вычислительными устройствами блока вычислений. С помощью мультиплексоров (рис. 8.2.1) линии четырех внутренних шин адреса и данных подключены к внешним выводам, образующим соответственно 24–разрядную внешнюю шину данных и 14–разрядную внешнюю шину адреса.

Системный интерфейс

Синхронизация процессора

Для синхронизации процессора могут быть использованы внешние синхроимпульсы, подаваемые на его внешний вывод CLKIN. Однако в большинстве случаев для формирования синхроимпульсов CLKIN к выводам CLKIN и XTAL процессора подключается кварцевый резонатор.

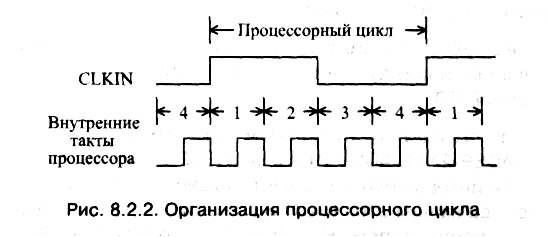

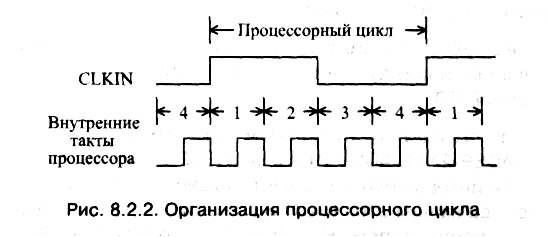

Период следования синхроимпульсов CLKIN (или тактовая частота) определяет длительность процессорного (командного) цикла.

Для разделения последовательности выполняемых микроопераций в течение процессорного цикла используются внутренние фазовые циклы с частотой в четыре раза превышающей тактовую частоту (рис. 8.2.2). Процессоры генерируют также внешние синхроимпульсы CLKOUT с периодом следования, равным длительности процессорного цикла.

Сброс

Операция сброса, выполняемая под действием сигнала ?RESET = 0, предназначена для начальной загрузки, или инициализации, процессора, т. е. для приведения всех узлов процессора в исходное состояние, при котором возможно нормальное его функционирование. При включении питания на вывод ?RESET микросхемы должен быть подан сигнал ?RESET = 0. Сброс может осуществляться и при включенном питании. Сигнал CLKOUT во время сброса генерируется процессором.

Состояние регистров после сброса приводится в таблицах (графа «Сброс») при рассмотрении их функций по мере изучения структурно–функциональной организации процессоров семейства ADSP–21XX.

Содержимое памяти программ и данных, задействованной под регистры, после сброса (если он происходит при включенном питании) остается неизменным. Содержимое регистров вычислительных устройств после сброса может быть любым. Если состояние вывода управления картой памяти ММАР = 0, после сброса происходит начальная загрузка внутренней памяти программ из внешней загрузочной памяти. Для процессоров, содержащих интерфейс с ведущим процессором, сброс может быть также выполнен установкой соответствующего бита в статусном регистре HSR7.

Программная начальная загрузка

Операция программной начальной загрузки, инициируемая установкой бита BFORCE = 1 в позиции SR.9 системного регистра (табл. 8.2.2), очищает контекст (содержимое регистров) процессора и инициализирует некоторые регистры (ASTSAT, SSTAT, IMASK, IFC, RBUF, TBUF). При выполнении этой операции все прерывания маскируются, автобуферизация выключается, последовательные порты и таймер остаются активными.

Внешние прерывания

В процессорах семейства ADSP–21XX предусмотрены средства для обслуживания внешних запросов на прерывание. Сигналы запроса прерывания подаются на отдельный вывод микросхемы ?IRQ2 и альтернативные выводы ?IRQ0, ?IRQ1 порта SPORTI. Запрос на прерывание обслуживается, если прерывание не замаскировано (соответствующий бит в регистре разрешения прерываний IMASK установлен в 1) и отсутствуют прерывания с более высоким приоритетом.

Процессор не распознает запрос, если он поступил во время исполнения команды, при которой происходит обращение к внешней памяти более одного раза. Прерывания фиксируются, но не обрабатываются в режиме предоставления внешних шин (?BG = 0) при отключенном режиме GO.

Обслуживание прерывания состоит в передаче управления по адресу вектора прерывания. Прерывания могут быть сконфигурированы как прерывания по уровню или как прерывания по спаду.

При обслуживании прерывания по уровню сигнал запроса поддерживается внешним устройством до тех пор, пока не будет выполнена подпрограмма обработки. Однако в самом конце подпрограммы сигнал запроса должен быть снят, чтобы предотвратить повторную обработку прерывания.

При обслуживании прерывания по спаду процессор фиксирует переход сигнала из высокого уровня к низкому. После этого сигнал запроса может быть снят. После обслуживания прерывания фиксация прерывания процессором автоматически снимается и процессор готов к обслуживанию другого запроса.

Выводы флагов

Входной флаг FI может использоваться в командах CALL и JUMP, характер выполнения которых зависит от состояния флага и определяется следующими условиями: IF FLAG_IN, IF NOT FLAG_IN. При этом учитывается последнее состояние флага. Например, условие IF FLAG_IN выполнено, если последнее состояние флага FI = 1. Выходные флаги FO и FL0, FL1, FL2 (в процессорах ADSP–21mps50, adsp–2111) могут использоваться для различных целей как выходной сигнал. Интерфейс с памятью.

Семейство процессоров ADSP–21XX использует модифицированную гарвардскую архитектуру, в которой память данных (RAM) хранит данные, A память программ (RAM и/или ROM) — команды и данные. Все версии кристаллов за исключением ADSP–2100 имеют внутреннюю память данных и программ. При необходимости объем памяти данных и программ может быть увеличен путем подключения внешней памяти. Если в кристаллах внутренняя память программ выполнена в виде RAM, используется процедура ее начальной загрузки из внешней загрузочной памяти.

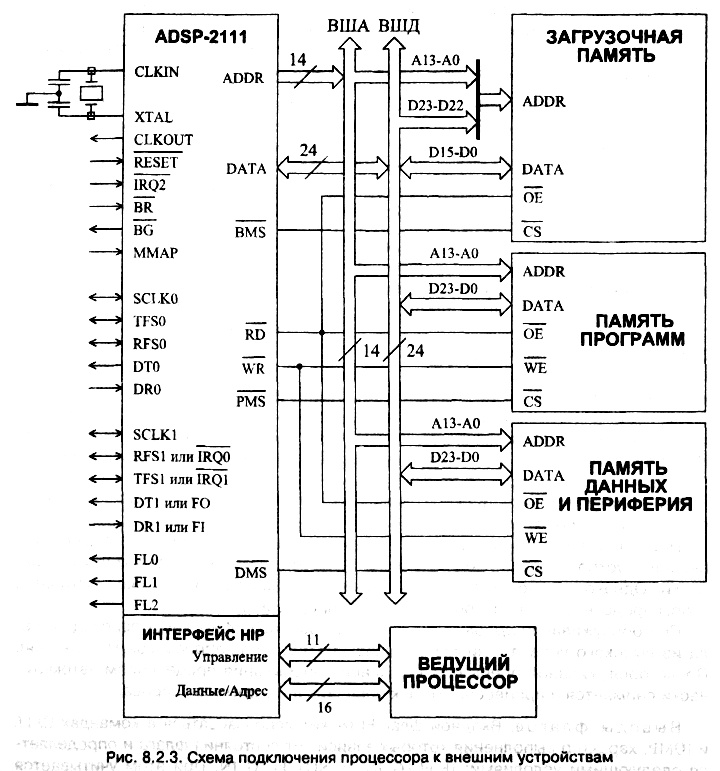

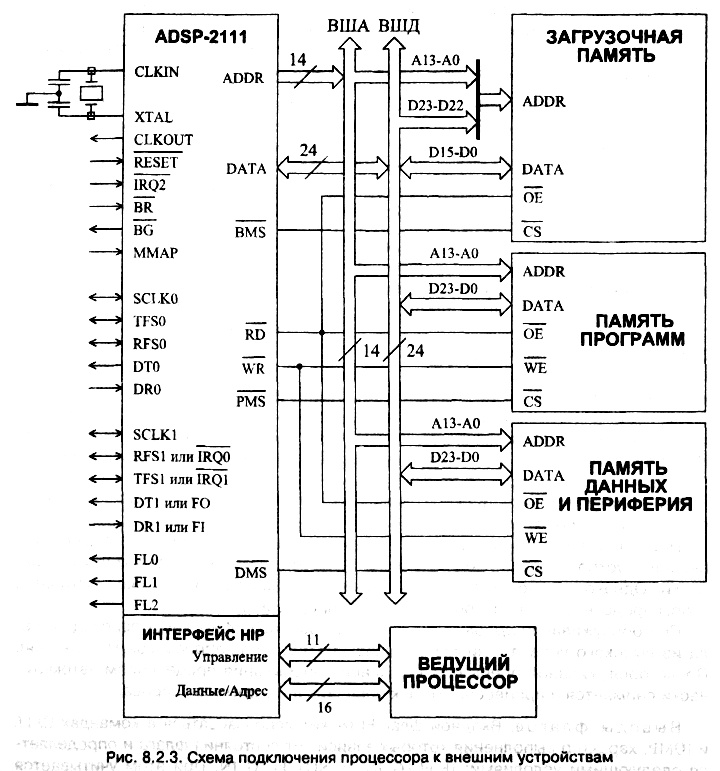

Схема процессора с внешней памятью приведена на рис. 8.2.3.

Интерфейс с загрузочной памятью

Если во время сброса сигнал управления картой памяти ММАР = 0 (Memory Map Control Signal — MMAP), начальная загрузка внутренней памяти начинается сразу после сброса из внешней загрузочной памяти. При ММАР = 1 начальную загрузку следует активизировать программно. Объем загрузочной памяти может составлять до 64К слов. Поэтому при обращении к ней используется 16–разрядный адрес.

Как видно из рис. 8.2.3, младшие 14 бит адреса выводятся с 14–разрядной шины адреса (A13–A0), старшие 2 бита — со старших двух линий шины данных (D23–D22). Байт данных считывается со средних восьми бит шины данных.  Загрузочная память состоит из восьми страниц длиной до 8К. Четвертый байт страницы содержит информацию о длине страницы: длина загрузочной страницы = (число 24–битных слов памяти команд/8) – 1. Каждый последующий четвертый байт страницы пустой.

Загрузочная память состоит из восьми страниц длиной до 8К. Четвертый байт страницы содержит информацию о длине страницы: длина загрузочной страницы = (число 24–битных слов памяти команд/8) – 1. Каждый последующий четвертый байт страницы пустой.

Каждый набор из трех байт между пустыми байтами представляет собой команду. При загрузке внутренней памяти программ сначала считывается длина страницы, затем производится загрузка байтов во внутреннюю память, начиная с верха страницы. Длина страницы должна быть кратна 8 байтам.

Самая короткая страница, длина которой равна нулю, содержит восемь слов, расположенных в 32 последовательных байтах (с учетом пустых) загрузочной памяти.

Если сигнал управления картой памяти ММАР = 1, возможна программная реализация начальной загрузки с любой из восьми страниц загрузочной памяти. Номер страницы задается битами BRAGE.0–BRAGE.2 (позиции SR.6–SR.8) системного регистра (табл. 8.2.2). Для инициирования загрузки следует установить бит BFORCE = 1 (позиция SR.9). В этом случае процессором автоматически вырабатывается строб ?ВМS = 0, который подается на вход выбора кристалла ?СS (рис. 8.2.3).

Число циклов ожидания (от 0 до 7, по умолчанию 3) для доступа к загрузочной памяти устанавливается трехразрядным кодом BWAIT.2…BWAIT.0 (позиции SR.3–SR5) системного регистра. При выполнении операции начальной загрузки генератор адресов загрузочной памяти формирует последовательность адресов для считывания соответствующих байтов из загрузочной памяти и записи их во внутреннюю память, начиная со старших адресов. Формат загрузочного адреса приведен на рис. 8.2.4.

Код загрузочного адреса состоит из четырех полей. В 3–битное поле старших разрядов из системного регистра заносится номер страницы. С

ледующее тюле; представляет собой 8–битную длину страницы, задаваемую в четвертом байте страницы.

В поле кода слова задается порядковый номер считываемого слова. В исходном состоянии поле содержит код 111, что соответствует 8–му слову.

Поле из двух младших разрядов задает код байта, считываемого из загрузочной памяти: старший байт USB = 00, средний байт MSB = 01 и младший байт LSB = 10. Байты учитываются в следующем порядке: старший, младший, средний. Пример. Рассмотрим операцию начальной загрузки восьми 24–разрядных слов (Слово 7, Слово 0) с самой короткой страницы, длина которой равна 0. Размещение слов В загрузочной памяти приведено в Табл. 8.2.3. Последовательность загрузки:

? шаг 1: читается четвертый байт, расположенный по адресу 0003. В этом байте указана длина страницы;

? шаг 2: считывается старший байт USB Слова 7, расположенный по адресу 001С;

? шаг 3: считывается младший байт LSB Слова 7, расположенный по адресу 001Е;

? шаг 4: считывается средний байт MSB Слова 7, расположенный по адресу 001D.

? после загрузки байта MSB Слова 7 во внутреннюю память программ происходит декрементация кода слова (пропускается ячейка с адресом 000В). Затем генерируются три последовательных адреса 0018, 001А, 0019 (шаги 5,6,7, см. табл. 8.2.3) для считывания трех байтов Слова 6 и т. д.

Процесс продолжается до тех пор, пока не будет считан средний байт MSB Слова 0 (шаг 25). Начальная загрузка внутренней памяти программ после сброса происходит так же, как программно–инициированная загрузка за исключением мелких деталей.

Интерфейс с памятью программ

В процессоре ADSP–21XX предусмотрены средства для обращения к внутренней и внешней памяти программ общим объемом 16К 24–битных слов (рис. 8.2.3). При обращении к внешней памяти программ используются:

? выход ?PMS процессора, на который выставляется строб ?PMS = 0 для активизации памяти программ;

? выходы ?RD/?WR процессора для чтения/записи памяти программ;

? 14–битная внешняя шина адреса (ВША) для адресации;

? 24–битная внешняя шина данных (ВШД) для вывода данных. При одновременном обращении к внешней памяти программ и памяти данных данные из памяти программ считываются первыми. С помощью трех бит PWAIT0–PWAIT2 в позициях SR0–SR2 системного регистра (табл. 8.2.2) задается число циклов ожидания для памяти программ. При обращении к внутренней памяти программ сигналы ?PMS, ?DMS. ?RD, ?WR имеют высокий уровень, исключающий возможность активизации микросхем внешней памяти, A внешние шины адреса и данных принимают высокоомное состояние. В этом режиме процессор способен за один цикл загрузить два операнда и следующую команду. Отображение адресного пространства памяти программ зависит от состояния вывода управления картой памяти ММАР. При ММАР = 0 в процессе начальной загрузки внутренней памяти программ внутренняя память (например, 2К) располагается по младшим адресам, A внешняя (14К) — по старшим; при ММАР = 1 — наоборот.

Интерфейс с памятью данных

В процессоре ADSP–21XX предусмотрены средства для обращения к внешней и внутренней памяти данных общим объемом 16К 16–битных слов. При обращении к внешней памяти данных используются (рис. 8.2.3):

? выход ?DMS процессора, на который выставляется строб ?DMS = 0 для активизации памяти программ;

? выходы ?RD/?WR процессора для чтения/записи памяти программ;

? 14–битная внешняя шина адреса (ВША) для адресации;

? 24–битная внешняя шина данных (ВШД) для вывода 16 старших бит данных. При обращении к внутренней памяти данных сигналы ?PMS, ?DMS, ?RD, ?WR имеют высокий уровень, исключающий возможность активизации микросхем внешней памяти, A внешние шины адреса и данных принимают высокоомное состояние.

Предоставление внешних шин периферийным устройствам (рис. 8.2.3).

Для получения контроля над внешними шинами периферийное устройство посылает сигнал запроса шины ?BR = 0 (Bus Request — BR), который в текущем или следующем цикле распознается процессором. В следующем цикле после распознавания процессор устанавливает сигнал предоставления шины ?BG = 0 (Bus Grant — BG), переводит шины адреса и данных в высокоомное состояние, A выводы ?PMS, ?DMS, ?RD, ?WR в единичное состояние.

После этого управление шинами передается периферийному устройству. В режиме предоставления шин (Grant Out — GO) последовательные порты и интерфейс HIP остаются активными.  Разрешение режима GO (бит G_MODE = 1 в позиции MSTAT.6 регистра режима и статуса процессора, табл. 8.3.3) позволяет процессору выполнить команды из внутренней памяти программ в то время, когда шина предоставлена другому устройству. Процессор перейдет в состояние ожидания только тогда, когда потребуется доступ к внешней памяти.

Разрешение режима GO (бит G_MODE = 1 в позиции MSTAT.6 регистра режима и статуса процессора, табл. 8.3.3) позволяет процессору выполнить команды из внутренней памяти программ в то время, когда шина предоставлена другому устройству. Процессор перейдет в состояние ожидания только тогда, когда потребуется доступ к внешней памяти.

При выключенном режиме GO процессор всегда переходит в состояние ожидания во время предоставления шины другому устройству. Внутреннее состояние процессора при этом не изменяется. После удовлетворения запроса процессор возобновляет работу с того места, где она была прервана. После сброса периферийным устройством сигнала запроса шины (?BR = 1) процессор отвечает сбросом сигнала предоставления шины (?BG = 1) и возвращает себе контроль над внешними шинами.

onetwoclick.ru

onetwoclick.ru