Блок микропрограммного управления – этот блок входит в состав управляющего автомата с программируемой логикой (см. рис. 1.4.1) и служит для модификации 3–разрядного адреса. Адресный код AD2AD1AD0, считываемый из комбинационной схемы памяти, поступает на входы БМУ. Если в «ячейке» памяти находится микрокоманда, связанная с проверкой логического условия (Х1, Х2 или ХЗ), и его значение при выполнении микрокоманды равно 1, то адресный код на выходе БМУ увеличивается на 1 :AD2′ AD1′ AD0′ = AD2 AD1 AD0 + 1.

Блок микропрограммного управления – этот блок входит в состав управляющего автомата с программируемой логикой (см. рис. 1.4.1) и служит для модификации 3–разрядного адреса. Адресный код AD2AD1AD0, считываемый из комбинационной схемы памяти, поступает на входы БМУ. Если в «ячейке» памяти находится микрокоманда, связанная с проверкой логического условия (Х1, Х2 или ХЗ), и его значение при выполнении микрокоманды равно 1, то адресный код на выходе БМУ увеличивается на 1 :AD2′ AD1′ AD0′ = AD2 AD1 AD0 + 1.

В других случаях код сохраняется:

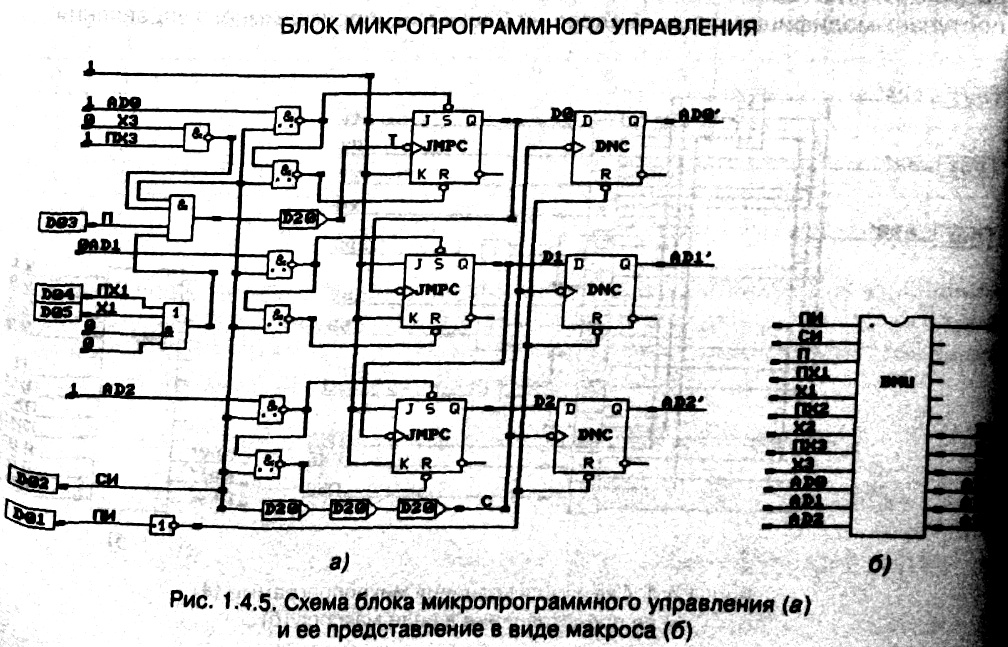

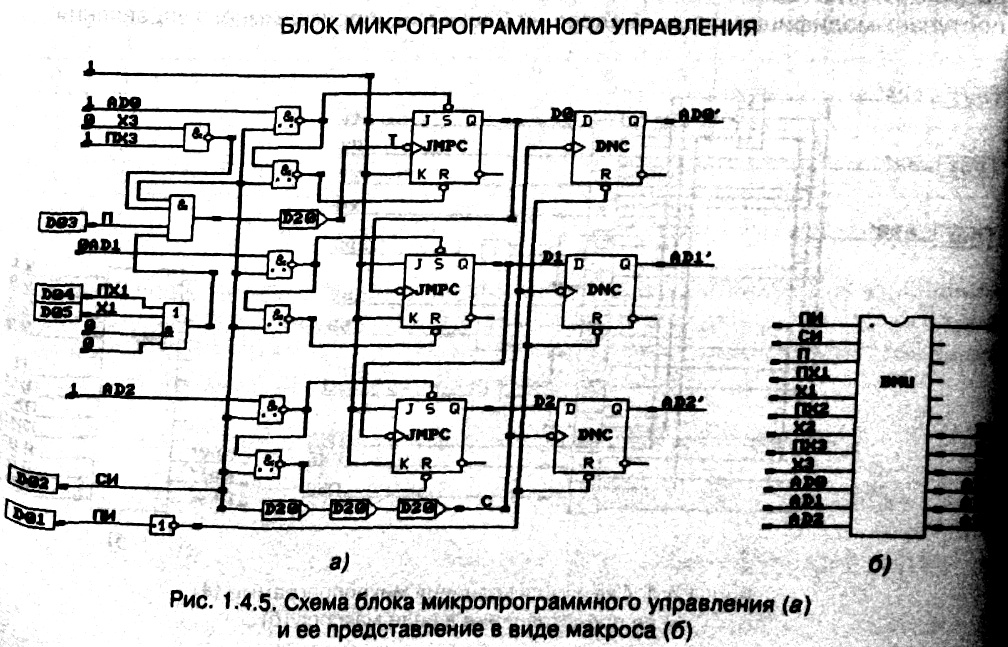

AD2′ AD1′ AD0′ = AD2 AD1 AD0. К этому случаю отнесена и проверка условия ХЗ, поскольку при ХЗ = 1 операция умножения завершается. В схеме БМУ (рис. 1.4.5, а) можно выделить три адресных канала и узел управления. Каждый адресный канал содержит:

- JK–триггер с асинхронными RS–входами для загрузки одного из разрядов (AD0, AD1, AD2) адреса. На J– и K– входы триггера поданы единичные сигналы, поэтому они работают в Т–режиме. Выходы первого (верхнего) и второго триггера подключены к тактовым Т–входам второго и третьего триггеров соответственно. В совокупности JK–триггеры образуют 3–разрядный счетчик с последовательным переносом;

- два элемента 2И–НЕ, образующих с асинхронными RS–входами схему D–триггера. Логические элементы управляются синхроимпульсами СИ. При СИ = 1 элементы открыты, и разряды адреса AD2 AD1 AD0 заносятся в JK–триггер. При СИ = 0 JK–триггер переводится в счетный режим, так как ? S = ? R = 1 и J = К = 1, для чего в цепь запуска счетчика включен элемент задержки (D20);

- D–триггер для временного хранения разряда адреса.

Узел управления состоит из логических элементов 2И–ИЛИ, 4И, 2И–НЕ. К узлу управления можно отнести инвертор и элементы задержки D20, обеспечивающие работу счетчика на JK–триггерах и загрузку D–триггеров с требуемой задержкой. В процессе умножения, когда ХЗ = 0, осуществляется проверка логических условий Х1 или Х2. Узел управления пропускает на тактовый вход Т синхроимпульс СИ, если выполняется одно из условий:

П . ПХ1 . X1 = 1 или П . ПХ2 . Х2= 1,

где П — сигнал, инициирующий проверку логических условий; ПХ1, ПХ2 — единичные сигналы указывающие по какому условию происходит проверка; Х1, Х2 — сигналы, информирующие о выполнении (при единичном значении) или невыполнении (при нулевом значении) логических условий (поступают из операционного автомата).

При поступлении на вход Т синхроимпульса СИ содержимое счетчика, составленного из JK–триггеров, увеличивается на 1, следовательно, происходит модификация адреса. Принцип работы БМУ. При считывании каждой микрокоманды из схемы памяти на входы БМУ поступают:

- ориентировочный адресный код AD2 AD1 AD0 (указан в поле адреса) следующей микрокоманды, который загружается по асинхронным SR–входам в JK–триггеры счетчика;

- сигналы П, ПХ1, ПХ2, ПХЗ (указаны в поле условий перехода), инициирующие проверку логических условий. В процессе умножения ПХЗ = 0, поэтому на один из входов логического элемента 4И поступает единичный сигнал, разрешающий проверку условий Х1 и Х2.

Из операционного автомата в БМУ поступают текущие значения Х1, Х2 сигналов логических условий.

Если для следующей микрокоманды необходима проверка логических условий, то П = 1 и логическое условие, по которому происходит проверка, ПХ1 = 1 (или ПХ2 = 1). В зависимости от текущего значение Х1 (Х2) возможны два исхода проверки:

- при X1 = 1 (Х2 = 1) с выхода логического элемента 4И на тактовый вход Т счетчика поступает синхроимпульс СИ и содержимое счетчика увеличивается на единицу. В этом случае с выходов БМУ в «ячейку памяти» записывается адрес AD2′ AD1′ ADO’ = AD2 AD1 ADO + 1;

- при Х1 = 0 (Х2 = 0) логический элемент 4И не пропускает синхроимпульс СИ на тактовый вход Т счетчика и его содержимое останется неизменным AD2′ AD1′ AD0′ = AD2 AD1 AD0, т. е. указанный в микрокоманде адрес сохраняется.

Проверка работоспособности БМУ

Цель проверки — выявить условия, при которых происходит изменение поступившего в БМУ адресного кода. Для этого достаточно рассмотреть реакцию БМУ при проверке одного условия (например, Х1) в двух режимах работы:

- проверка логических условий не инициирована (П = 0). В этом случае при любых комбинациях сигналов ПХ1 и Х1, поступающих на вход элемента 2И–ИЛИ должно выполняться равенство AD2 AD1 AD0 = AD2′ AD1′ AD0′ — адресный код сохраняется;

- проверка инициирована по условию Х1 (П = 1, ПХ1= 1). В этом режиме при Х1 =0 адресный код должен сохраняться (AD2 AD1 AD0 = AD2′ AD1′ AD0′), а при Х1 = 1 — изменяться (AD2′ AD1′ AD0′ = AD2 AD1 AD0 + 1).

Условия проверки:

- на адресные входы БМУ подается код AD2 AD1 ADO = 101;

- логическое условие Х3 = 0, так как с появлением сигнала операция умножения завершается;

- проверяется только логическое условие Х1, поэтому на выходы нижней схемы И логического элемента 2И–ИЛИ поданы нулевые сигналы. Для проверки работы БМУ использовались следующие генераторы (рис. 1.4.5, а);

- генератор D01, формирующий на первом такте пусковой импульс ПИ = 1 для сброса D–триггеров на первом такте;

- генератор 02, с выхода которого снимаются синхроимпульсы СИ для загрузки JK– и D–триггеров адресным кодом и активизации работы счетчика;

- генераторы D03, D04 сигналов П, ПХ1, инициирующих проверку логического условия X1;

- генератор D05, имитирующий текущее значение логического условия X1.

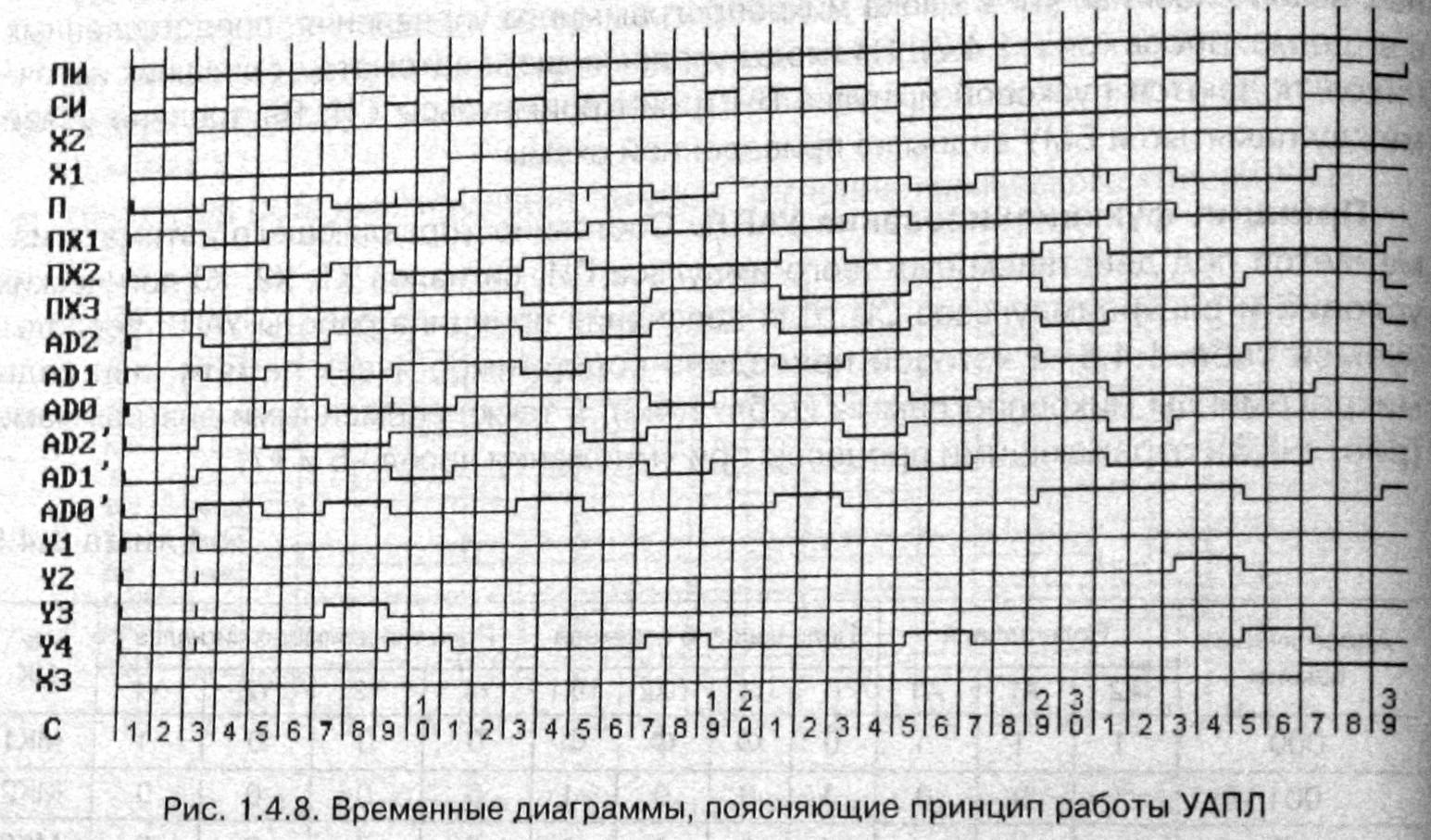

Результаты проверки приведены в виде временных диаграмм на рис. 1.4.6. В течение первых четырех периодов синхроимпульсов (такты 1–8) проверялась работа БМУ при П = 0, а в течение четырех последующих (такты 9–16) — при П = 1 для четырех возможных комбинаций сигналов ПХ1 и Х1.

После первого синхроимпульса на выходе БМУ появляется адресный код А D2′ А D1′ А D0′ = А D2 А D1 А D0 =101, который сохраняется до 17–го такта. На 16–м такте при П = ПХ1 = Х1 = 1 на вход счетчика поступает импульс Т, по срезу которого (такт 17) происходит с некоторой задержкой увеличение адреса на единицу. На выходе БМУ формируется адресный код А D2′ А D1 А D0′ = 110. При сохранении сигналов П = ПХ1 = Х1 = 1 адрес остается неизменным (такты 18–20), поскольку на вход по–прежнему подается А D2 А D1 А D0 = 101.

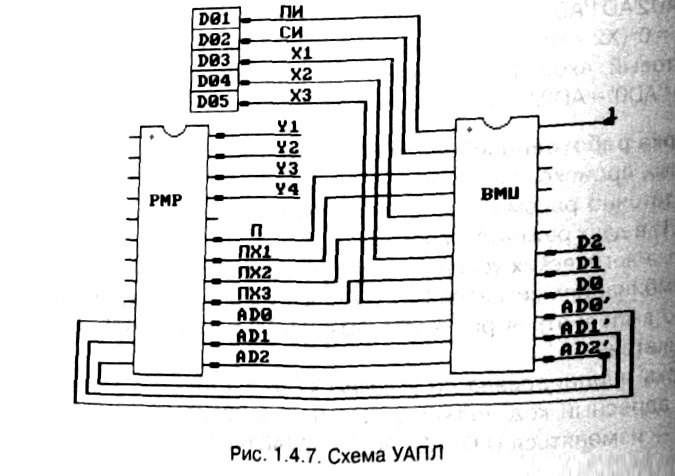

На рис. 1.4.5, б приведена схема БМУ в виде макроэлемента.

Управляющий автомат с программируемой логикой составлен из рассмотренных выше схем памяти и блока микропрограммного управления, представленных в виде макросов (рис. 1.4.7). На входы управляющего автомата от внешних источников подаются пусковой импульс ПИ и синхроимпульсы СИ. Внутренние связи между памятью и БМУ видны из приведенной схемы.

Принцип функционирования УАПЛ. Состояние управляющего автомата изменяется под действием пускового импульса ПИ, сигналов Х1, Х2, Х3 логических условий и синхроимпульсов СИ. Для пояснения принципа работы УАПЛ воспользуемся табл. 1.4.5, в которой приведено содержимое ячеек памяти, или коды микрокоманды микропрограммы (табл. 1.4.3), а также временными диаграммами (рис. 1.4.8), отражающими процессы при умножении чисел –5 и +7.

С помощью пускового импульса ПИ происходит сброс D–триггеров в БМУ, в результате чего формируется адресный код А2′ А1′ А0′ = 000, и с выходов комбинационной схемы памяти микропрограмм (рис. 1.4.4, а) снимается 11–разрядный код первой микрокоманды микропрограммы (МК1). В поле адреса этой микрокоманды (табл. 1.4.5) указан адрес ячейки А2 А1 А0 = 111, а в поле управляющих сигналов

Y1 = 1. Поэтому после первого СИ в операционном автомате выполняется микрокоманда МК1 начальной установки регистров, триггера и счетчика, а из памяти считывается содержимое ячейки 111 (МК8).

В поле адреса ячейки 111 указан адрес ячейки 001, а в поле условий перехода П = 1, ПХ2 = 1. Поэтому вторым СИ производится проверка логического условия Х2 :

- при Х2 = 0 адрес ячейки сохраняется, т.е. с выхода БМУ снимается код А2′ А1′ А0′ = 001. Из ячейки 001 считывается микрокоманда МК2 микропрограммы, в адресном поле которой указан адрес ячейки А2 А1 А0 = 100, а в поле условий перехода значения П = 1, ПХ1 = 1, инициирующие проверку логического условия Х1 (младшего разряда регистра RG2);

- при Х2 = 1 адрес ячейки А2 А1 А0 = 001 увеличивается на 1, а из ячейки с адресом А2 А1 А0 = 010 считывается микрокоманда МКЗ микропрограммы, в адресном поле которой указан адрес ячейки А2 А1 А0 – 100, а в поле условий перехода П = 1, ПХ1 = 1, инициирующие, как и в предыдущем случае, проверку логического условия Х1.

Поскольку после начальной установки операционного автомата значение младшего разряда регистра RG2 равно P0 = Х2 = 1, а значение Х1 = 0 следующими микрокомандами являются МКЗ и МК4 (см. рис. 1.4.2).

При Х2 = 0 на срезе третьего СИ выполняется микрокоманда микропрограмма проверки логического условия Х1 из ячейки с адресом 100:

- при X1 = 0 адрес ячейки сохраняется (А2′ А1′ А0′ = 100). В этом случае на срезе четвертого импульса выполняется микрокоманда Y3 сдвига содержимого RG3, RG2. Так как в поле адреса ячейки 100 указан адресный код 001, после завершения микрокоманды Y3 начинается новый цикл выполнения микропрограммы;

- при X1 = 1 исходный адрес А2 А1 А0 = 100 увеличивается на 1 и из ячейки с адресом 101 считывается микрокоманда микропрограммы. В этом случае на срезе четвертого импульса выполняется микрокоманда Y2 арифметического сложения содержимого регистров RG1 и RG3 с помещением результата в RG3. В поле адреса ячейки 101 указан адресный код 100, после завершения микрокоманды Y2 выполняется микрокоманда Y3 сдвига и лишь тогда начинается новый цикл выполнения микропрограммы.

Проверка работоспособности УАПЛ. Для проверки работы УАПЛ используются генераторы D01/ D05. Генератор D01 вырабатывает пусковой импульс ПИ = 1 на первом такте; генератор D02 — синхроимпульсы СИ; генераторы D03, D04, D05 входные сигналы X1, Х2, ХЗ логических условий. При моделировании сигналы X1, Х2, ХЗ выбраны согласно алгоритму умножения чисел (–5)10 и +710. Из временных диаграмм (рис. 1.4.8) следует, что на выходе УАПЛ формируется последовательность микрокоманд, которая дает правильный результат перемножения операндов А = 1011 и В = 0111 при совместном использовании УАПЛ и операционного автомата в процессорном устройстве (см. рис. 1.5.4).

onetwoclick.ru

onetwoclick.ru