Общие сведения.

Общие сведения.

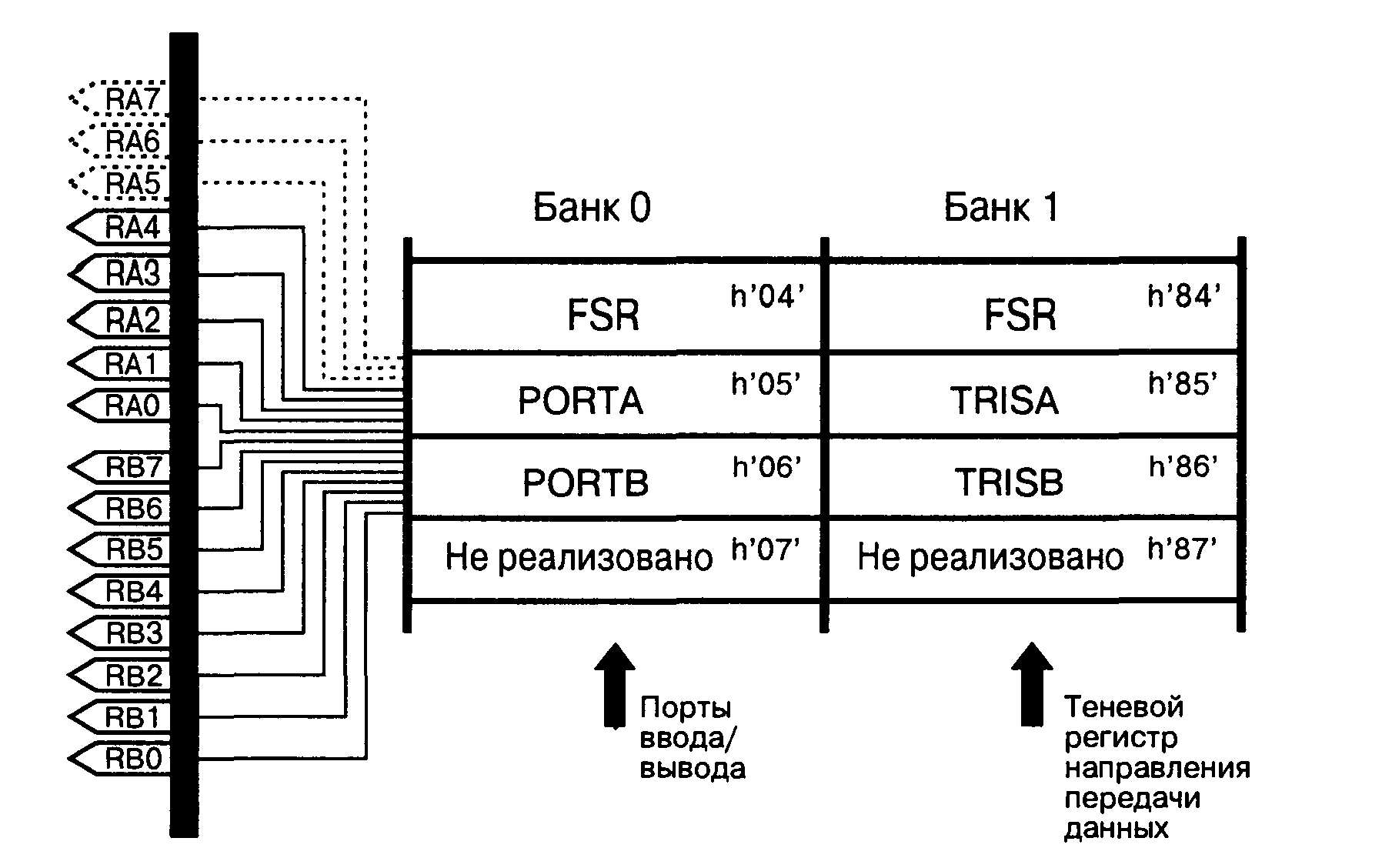

Через параллельные порты реализуется основной интерфейс между микроконтроллером и внешними устройствами. Количество линий ввода/вывода

8–разрядных микроконтроллеров равно 8. В карте памяти микроконтроллера каждый порт ввода/вывода представлен регистром данных порта. Для обращения к регистру данных при организации обмена в параллельном формате используются те же команды, что для обращения к ячейкам резидентной оперативной памяти. Доступ к отдельным разрядам портов осуществляется специальными командами, которые называются командами битового процессора.

По функциональному признаку

параллельные порты разделяют на три группы:

? однонаправленные порты, предназначенные для передачи информации в одном направлении (только для ввода или только для вывода);

? двунаправленные порты, позволяющие задавать направление передачи всех линий и каждой линии в отдельности. В случае необходимости каждая линия может быть сконфигурирована индивидуально и обслужена командами битового процессора независимо от других линий того же порта ввода/вывода;

? порты с альтернативными функциями, которые определяются состоянием микроконтроллера. Отдельные линии таких портов связаны со встроенными в микроконтроллер периферийными модулями (таймером, АЦП, контроллером, последовательным приемопередатчиком и др.), при этом:

• если модуль активизирован, то задействованные линии ввода/вывода порта автоматически конфигурируются в соответствии с функциональным назначением в модуле и не могут быть использованы по другому назначению;

• если же периферийный модуль МК не используется, то его выводы можно задействовать как обычные линии ввода/вывода порта.

Альтернативную функцию могут иметь линии однонаправленных и двунаправленных портов.

Структурно–функциональные особенности портов.

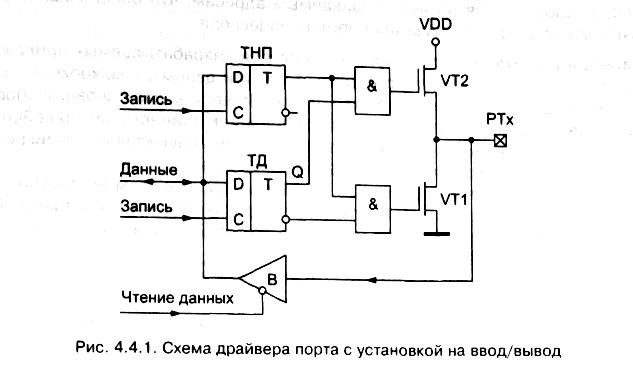

Рассмотрим схемотехнику портов ввода/вывода на уровне одной линии. Совокупность аппаратных средства, обслуживаемых одну линию порта называют драйвером порта. Рассмотрим основные типы двунаправленных драйверов (или линий ввода/вывода).

Драйверы с установкой на ввод/вывод.

Схема такого драйвера приведена на рис. 4.4.1. Настройка драйвера на ввод/вывод осуществляется установкой бита в специальном триггере направления передачи (ТИП). Нулевое значение бита конфигурирует драйвер на ввод, единичное — на вывод.

Режим ввода данных

автоматически устанавливается после сброса микроконтроллера. В исходном состоянии триггер направления передачи ТНП и триггер данных ТД находятся в нулевом состоянии, с выходов логических элементов И снимаются нулевые уровни сигналов, транзисторы

VT

1 и

VT

2 заперты и не влияют на процесс ввода. При вводе данных:

? на управляемый буфер В подается сигнал чтения данных (

RD

# = 0, где # — знак инверсии), открывая его;

? поступающие на вывод РТх данные передаются непосредственно на внутреннюю линию Данные, минуя триггер данных ТД.

Режим вывода данных

инициируется путем установки триггера направления передачи ТНП в единичное состояние, после чего на один из входов логических элементов И поступает единичный уровень и управление транзисторами

VT

1 и

VT

2 выходного каскада порта передается триггеру данных ТД. Если на прямом выходе ТД установлен сигнал

Q

= 1, то открыт транзистор

VT

2 и на выходе контроллера РТх = 1. При

Q

= 0 открыт транзистор

VT

1 и РТх = 0.

Рассмотренное техническое решение реализовано в микроконтроллерах НС08 фирмы

Motorola

. Его достоинство — высокоомный вход в режиме ввода, недостаток — наличие триггера направления передачи.

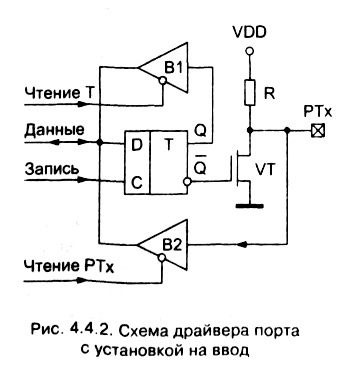

Драйверы с установкой на ввод.

Схема драйвера, требующего предварительную установку только на ввод данных, приведена на рис. 4.4.2.

Режим ввода данных

инициируется установкой триггера Т в состояние

Q

=1. Состояние триггера Т контролируется с помощью буфера В1. В этом режиме транзистор

V

Т1 заперт сигналом с инверсного выхода триггера. Данные в микроконтроллер поступают через буфер В2. Сопротивление со стороны вывода РТх определяется значением резистора

R

. После сброса микроконтроллер автоматически устанавливается в режим ввода. По сути дела, режим ввода соответствует режиму вывода единичного бита.

Режим вывода данных

не требует никаких предварительных установок:

? при выводе нулевого бита триггер Т переводится в состояние

Q

= 0, отпирается транзистор

VT

и с выхода РТх снимается сигнал с низким уровнем;

? при выводе единичного бита триггер Т переводится в состояние

Q

=1, транзистор

VT

запирается и с выхода РТх снимается сигнал с высоким уровнем. Рассмотренное техническое решение реализовано в микроконтроллерах

MCS

51 фирмы

Intel

. Его недостаток — низкое входное сопротивление в режиме ввода, обусловленное необходимостью использования подтягивающего к 1 резистора

R

для вывода единичного бита.

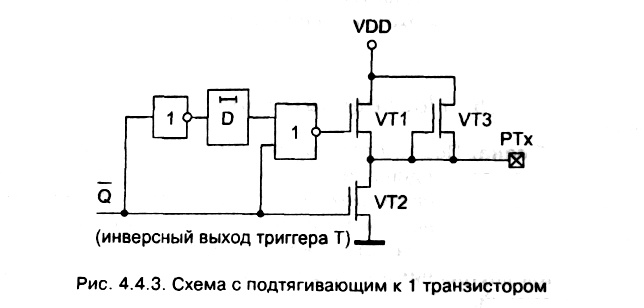

Драйверы с управляемыми подтягивающими резисторами.

Для устранения указанного выше недостатка в схему драйвера вводится управляемый подтягивающий резистор. Одно из таких технических решений приведено на рис. 4.4.3.

В качестве нагрузки выходного каскада используются транзисторы

VT1

и

VT3.

Управляемый транзистор

VT1

обладает сопротивлением в сотни раз меньшим по сравнению с транзистором

VT3.

Он обеспечивает быстрое переключение схемы и большую амплитуду импульса при выводе единичного бита. Транзистор

VT3

выполняет функцию подтягивающего резистора в установившемся режиме, его сопротивление значительно больше, чем

R

в схеме на рис. 4.4.2. При выводе единичного бита с появлением

Q# =

0 отпирается транзистор

VT1

и на выходе формируется логический уровень РТх = 1. Через некоторое время на выходе элемента задержки

D

появляется единичный сигнал, который переводит транзистор

VT1

в запертое состояние.

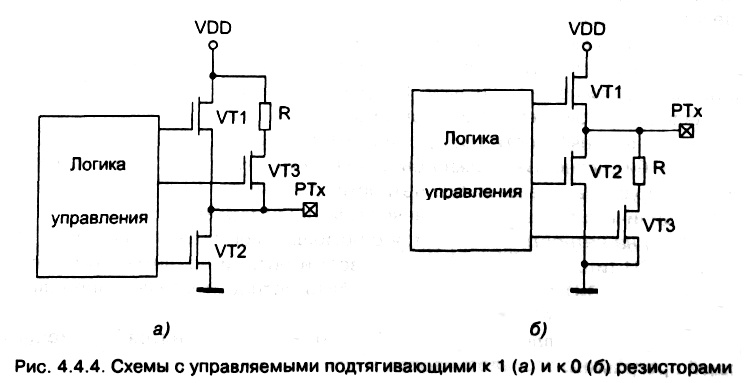

На рис. 4.4.4 приведены общие технические решения с управляемыми подтягивающими резисторами. В схеме на рис. 4.4.4, а резистор

R

с помощью

VT

3 подключается параллельно нагрузочному транзистору

VT

1, что позволяет при выводе данных подтягивать логический уровень к 1. В схеме на рис. 4.4.4, б резистор

R

подключается параллельно транзистору

VT

1, что позволяет подтягивать логический уровень к 0. Приведенные схемы используются в контроллерах фирмы

Motorola

.

В контроллере имеются средства программного подключения подтягивающих резисторов:

? специальный бит регистра конфигурации разрешает подключение резистора

R

;

? биты 0–7 регистра входного сопротивления непосредственно подключают

R

к требуемой линии. Значение бита можно многократно изменять в ходе выполнения прикладной программы. Следовательно, имеется возможность динамического управления входным сопротивлением по каждой линии порта ввода.

onetwoclick.ru

onetwoclick.ru