Прерывание в микропроцессорах (

Прерывание в микропроцессорах (

interruption

) — это событие, вызывающее прекращение работы основной программы и переход к выполнению процедуры, или подпрограммы, предназначенной для его обработки. Совокупность аппаратных средств, команд и программ обслуживающих прерывания образуют систему прерываний. Прерывание инициируется специальным сигналом, при появлении которого система прерываний изменяет ход выполнения программы. Можно выделить три вида прерываний:

?

аппаратные прерывания, которые инициируются внешними устройствами с помощью сигнала запроса на прерывание;

? программные

прерывания, которые инициируются специальными командами (например, командой

CALL

вызова подпрограммы);

? исключения,

вызванные возникновением особых условий (случаев) выполнения текущей команды (например, деление на нуль).

Прерывания используются:

? для обмена информацией между процессором и внешним устройством (ВУ);

? в аварийных ситуациях, например, при понижении напряжения питания. Обработка прерывания при отказе в системе питания должна выполняться в первую очередь, так как прерывающая подпрограмма поможет сохранить наиболее ценные результаты работы;

? при исключительных условиях, таких, как переполнение и антипереполнение при выполнении операции с плавающей точкой;

? для индикации аппаратных сбоев, приводящих к ошибкам при обработке данных (например, к ошибкам обнаруженным при контроле на четность);

? при программных сбоях, т. е. если предпринимаются попытки выполнить неверную или неопределенную команду, либо осуществить обращение к несуществующей или защищенной памяти;

? для координации работы в многопроцессорных системах;

? для профилактики, ремонта, тестирования и отладки системы. Прерывание позволяет перейти на ручное управление, например, с лицевой панели реализовать пошаговое выполнение программы. В дальнейшем основное внимание уделено аппаратным прерываниям, используемым для обмена информацией между процессором и ВУ. Обслуживание ВУ по прерываниям является альтернативой программно–управляемому обмену информацией. Рассматриваются общие принципы организации прерываний.

Последовательность обслуживания прерываний.

При обмене информацией по прерываниям инициатором обмена является внешнее устройство, которое подает специальный сигнал ЗАПРОС ПРЕРЫВАНИЯ (ЗПр) на соответствующий вход процессора. По завершении текущей команды процессор прекращает работу по основной программе, вырабатывает сигнал ПОДТВЕРЖДЕНИЕ ПРЕРЫВАНИЯ (ППр) и переходит к подпрограмме обработки прерывания, передавая ей начальный (стартовый) адрес, называемый точкой входа в процедуру. После выполнения подпрограммы происходит возврат к основной программе. Процесс обработки запроса на прерывание во многом подобен процессам вызова подпрограммы и возврата в основную программу. Однако вместо использования команд

(CALL, RET)

он реализуется аппаратным способом. Поэтому запросы на прерывания часто называют аппаратными вызовами подпрограмм.

При обслуживании прерывания можно выделить следующие основные этапы:

? прием запроса

на прерывание и его подтверждение;

? сохранение состояния процессора,

а именно, содержимого счетчика команд и основных программно доступных регистров процессора (аккумулятора, регистров общего назначения, статусных и других регистров) на время обработки прерывания с тем, чтобы обеспечить возможность возобновления работы по прерванной программе;

? идентификация

источника прерывания;

? непосредственное выполнение программы обработки прерывания; восстановление исходного состояния процессора, или содержимого основных регистров процессора;

? возврат

к основной программе.

Рассмотрим особенности некоторых этапов.

Управление входами и способы приема сигналов запроса на прерывания.

Микропроцессоры могут иметь разное количество входов запроса на прерывания (от одного и более). За каждым входом закреплен собственный стартовый адрес обслуживающей подпрограммы. Увеличение числа входов (линий) запросов позволяет организовать радиальную систему прерываний для обслуживания нескольких истопников прерываний. Часть из них может быть отведена для внутренних запросов прерываний (исключений), которые используются при возникновении нештатных ситуаций, например, при понижении напряжения питания.

Для управления входами запроса используются команды, позволяющие:

? сформировать маслу, биты которой индивидуально разрешают или запрещают (маскирует) запросы прерывания. Маска хранится в специальном регистре. Команды обеспечивают установку нового состояния маски;

? считывать текущее состояние маски в аккумулятор или другой регистр;

? управлять общим флагом разрешения/запрещения прерываний.

Известно три способа приема сигналов запросов:

? статический

способ, при котором сигнал фиксируется при появлении высокого уровня и остается активным в течение всего времени его действия. Последнее обстоятельство может привести к повторной фиксации уже принятого к обслуживанию запроса. Указанный недостаток может быть устранен блокировкой входа с помощью дополнительного триггера;

? динамический

способ, при котором запрос на прерывание фиксируется при каждом переходе сигнала из 0 в 1. Запрос сохраняется до тех пор, пока не будет обслужен или сброшен командой. Недостаток — низкая помехоустойчивость: любая помеха на входе может вызвать прерывание. Фиксация происходит даже при маскировании прерываний;

? комбинированный

способ, при котором для фиксации запроса используется два условия:

• изменение сигнала из 0 в 1;

• сохранение в течение некоторого времени высокого уровня сигнала, чтобы устранить влияние помех.

Входы запроса на прерывание процессор проверяет в конце командного цикла. При обнаружении запроса на прерывание и отсутствии маскирования процессор приступает к его обслуживанию, в противном случае продолжает выполнение основной программы.

Способы сохранения и восстановления состояния процессора.

Для возобновления работы прерванной (основной) программы необходимо на время обслуживания прерывания сохранить состояние процессора. Состояние процессора в любой момент характеризуется:

? содержимым счетчика команд и всех регистров процессора;

? состоянием всех сигналов управления.

Только в случае сохранения состояния процессора после обслуживания запроса на Прерывание работа прерванной программы будет продолжена, как будто ничего не произошло. При наличии прерывания должно быть сохранено текущее значение счетчика, являющееся адресом следующей команды основной программы, а также содержимое всех регистров, состояние которых может быть нарушено при выполнении прерывающей подпрограммы. После завершения подпрограммы, обслуживающей внешнее устройство, состояния счетчика и регистров должно быть восстановлено. Что касается сигналов управления, то они не могут быть сохранены, так как сама же операция по сохранению этих сигналов привела бы к их изменению. Однако перед началом каждого нового командного (машинного) цикла сигналы управления принимают определенное исходное состояние. По этой причине контроль сигналов запроса на прерывание процессор производит в самом конце каждого командного цикла.

Для сохранения состояния процессора во время выполнения подпрограммы используются следующие способы:

? блокирование основных регистров

и выполнение подпрограммы в другом наборе (банке) регистров. Этот способ обладает наибольшим быстродействием, однако его реализация возможна только при наличии в процессоре двойного набора регистров;

? пересылка

на хранение с последующим возвратом содержимого счетчика команд и программно доступных регистров во внешнюю оперативную память с обычным способом записи и считывания информации;

? пересылка

на хранение с последующим возвратом содержимого счетчика команд и программно доступных регистров во внешнюю (внутреннюю) оперативную память организованную как стек. Этот способ находит наиболее широкое применение.

Процедура изъятия из процессора содержимого счетчика и программно–доступных регистров перед началом обслуживания ВУ или восстановление содержимого перед возвратом в прерванную программу называется контекстным переключением.

Контекстные переключения выполняются с помощью пар команд типа

PUSH

,

POP

или

PUSH

A, POPA

(позволяют сохранить в стеке, а затем восстановить содержимое всех регистров).

Большинство процессоров автоматически сохраняет некоторую информацию о состоянии процессора. Например, все процессоры сохраняют текущее значение счетчика команд;

Motorola

6800 сохраняет в стеке содержимое всех своих регистров.

Способы идентификации источника прерывания.

Запрос на прерывание может поступать от нескольких внешних устройств (ВУ). Если каждое из ВУ подключено к отдельному входу запроса микропроцессора, проблемы определения источника прерываний не существует. Она возникает тогда, когда число ВУ превышает число входов запроса. Известно два наиболее распространенных способа идентификации источника прерывания: программный и аппаратный.

Программный способ

базируется на использовании главной программы обработки прерываний, которая при поступлении запроса производит последовательный программный опрос каждого ВУ до тех пор, пока не обнаружит устройство, пославшее запрос. Такой способ идентификации ВУ называют опросом, или поллингом (

POLL

). Обычно он используется при объединении запросов от нескольких источников с помощью элемента ИЛИ и передаче их по одной линии на вход процессора. Главная программа обработки прерываний содержит стандартные подпрограммы проверки готовности каждого внешнего устройства к обмену данными по состоянию сигнала запроса ЗПр, поступившего от него.

Каждому ВУ выделяется отдельный порт состояния (со своим адресом), в котором отводится бит для хранения значения сигнала запроса. Когда по общей линии поступает сигнал запроса, процессор завершает цикл и начинает последовательно опрашивать порты состояния. При обнаружении сигнала ЗПр = 1 основная программа передает управление подпрограмме обслуживания ВУ. При одновременном запросе на прерывание от нескольких ВУ обслуживается устройство, которое опрашивается первым. Таким образом, приоритетность обслуживания определяется позицией устройства в списке опроса.

Поллинг подобен обычной проверке сигнала готовности ВУ, которая используется при программно–управляемом обмене данными. Процессор опрашивает каждый из источников прерываний, пока не обнаружит тот, который послал запрос.

Преимущество использования поллинга в системах прерывания (по сравнению с системами без прерываний) состоит в том, что при наличии запроса один из входов всегда является активным. Для реализации поллинга требуются лишь адресуемые порты (регистры, триггеры). Поллинг целесообразно использовать при небольшом числе источников прерывания. Система прерываний с программным опросом, или поллинговая система прерываний, позволяет расширить число источников радиальной системы прерываний. Ее недостаток — задержка начала обслуживания ВУ, связанная с опросом.

Аппаратный способ

идентификации источников прерываний базируется на схемной реализации опроса ВУ. При обнаружении ВУ, запросившего прерывание, в процессор посылается его собственный код, который называют вектором прерывания. Название связано с тем, что двоичный

n

–разрядный код можно представить вектором в

n

–мерном пространстве. Вектор прерывания является начальным, или стартовым адресом подпрограммы. Системы прерываний с аппаратной идентификацией ВУ называют векторными системами прерываний. Простейшей векторной системой прерываний является система, к каждому входу запроса на прерывание которой подключено по одному ВУ. Такая система, как указано выше, не требует идентификации ВУ. Принципы построения векторных систем прерываний рассмотрены ниже.

Способы передачи управления.

После идентификации источника запроса на прерывание центральный процессор должен передать управление подпрограмме обслуживания ВУ, пославшего запрос. Перейти к подпрограмме можно путем:

? выполнения команды ПЕРЕХОД К ПОДПРОГРАММЕ (

CALL

) или РЕСТАРТ

(

TRAP

) с заданным адресом (способ использовался в

Intel

4040);

? выбора из определенного регистра или определенной ячейки памяти нового значения счетчика команд, соответствующего адресу подпрограммы (использовался в

Motorola

6800,

RCA CDP1802);

? выполнения команды ПЕРЕХОД К ПОДПРОГРАММЕ с адресом, который определяется внешним устройством (способ использовался в

Signetics

2650);

? использования выходного сигнала ПОДТВЕРЖДЕНИЕ ЗАПРОСА НА ПРЕРЫВАНИЕ предоставить шину данных для помещения на нее адреса внешнего устройства, пославшего запрос. При этом доступ к памяти и другим ВУ должен быть заблокирован (способ использовался в КР580ВМ80). Первый и второй способы не требует больших аппаратных затрат, но не позволяет идентифицировать источник прерывания. Любой из них требует работы с подпрограммами. Третий и четвертый способы более гибкие, но требуют аппаратных затрат.

По завершении обслуживания запроса на прерывание ЦП должен вернуться для продолжения выполнения основной программы. Для этого используется команда возврата из подпрограммы

RET.

Схемная идентификация источников прерывания.

Рассмотрим некоторые схемные способы определения источников прерывания.

Способ последовательного опроса.

Один из возможных вариантов схемной реализации системы прерываний с последовательным опросом представлен на рис. 3.8.1. В состав системы входят счетчик

CT,

дешифратор

DC

, логический элемент И–ИЛИ и триггер запроса ТЗ. Полагаем, что ТЗ сброшен, сигналы запросов на прерывание ЗПр1, …, ЗПрN от ВУ на входах И–ИЛИ отсутствуют (их значения равны нулю). Счетчик

CT,

на вход которого поступают синхроимпульсы СИ, через дешифратор производит последовательный циклический опрос входов элемента И–ИЛИ. С поступлением запроса от одного из ВУ (например ЗПр

k

) триггер запроса ТЗ устанавливается в единичное состояние. Выходной сигнал ТЗ останавливает счетчик и вызывает прерывание микропроцессора. Содержимое счетчика фиксирует код (номер к) запрашиваемого ВУ. Прерывающая программа открывает буфер для считывания кода ВУ. Принятый код (номер к) используется для формирования адреса подпрограммы обслуживания и информирования ВУ о начале обслуживания прерывания. Внешнее устройство снимает запрос и начинает готовить новую порцию данных.

Триггер запроса ТЗ сбрасывается программно в конце обработки прерывания, после чего процесс повторяется.

Способ параллельного опроса.

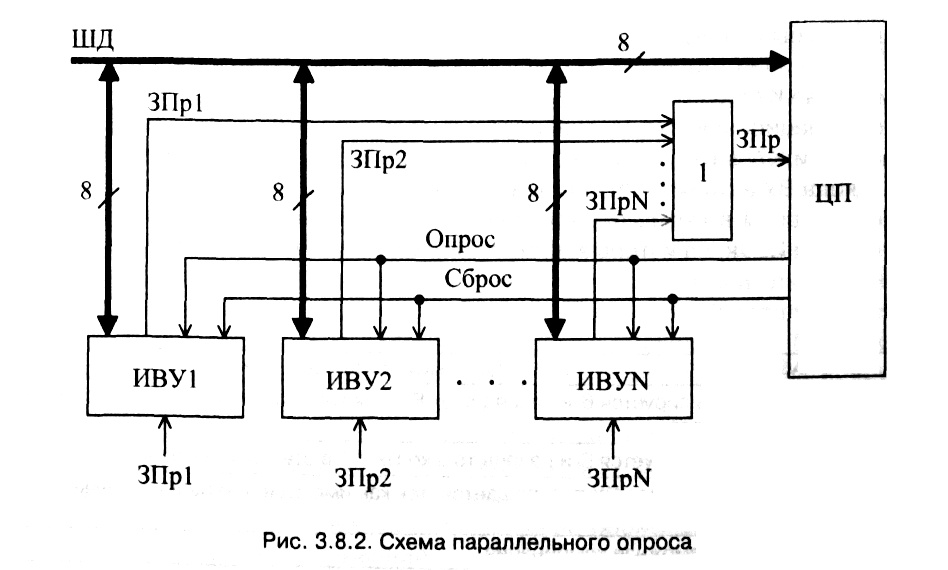

Для ускорения идентификации ВУ используют способ параллельного опроса, общая схема которого приведена на рис. 3.8.2. В ее состав входят интерфейсы внешних устройств (ИВУ1…ИВУN) и логический элемент ИЛИ.

Схема ИВУ раскрыта на рис. 3.8.3. Интерфейс ВУ содержит:

? триггер запроса ТЗ для временного хранения запросов на прерывания от ВУ;

? регистр приоритетов для хранения восьмиразрядного двоичного кода ВУ, причем коды не должны повторяться и чем больше значение кода в десятичном исчислении, тем выше приоритет ВУ;

? анализаторы разрядов АР0…АР7 кода ВУ;

? дополнительные логические элементы.

Поступившие от ВУ один или несколько запросов на прерывание фиксируются в триггере запроса ТЗ соответствующего интерфейса ИВУ

k

. На выходе элемента ИЛИ формируется единственный запрос ЗПр, который принимает ЦП (рис. 3.8.2).

В ответ на принятый запрос ЦП посылает сигнал Опрос = 1, который выполняет две функции (рис. 3.8.3):

? блокирует доступ к триггерам ТЗ, чтобы сохранить постоянное число запросов во время цикла опроса;

? в каждом ИВУ открывает схему совпадения для формирования сигнала А7 = 1 активизации начала анализа старшего разряда Р7 кода ВУ, который хранится в регистре приоритета.

Если хотя бы для одного из принятых запросов старший разряд Р7 кода ВУ равен 1, то на линии старшего разряда ШД устанавливается сигнал К7 = 1, в противном случае К7 = 0.

В комбинационной схеме анализатора разрядов АР7 происходит обработка сигналов Р7 и К7, в результате которой формируется сигнал А6 для анализа 6–го разряда кода ВУ в схеме АР6 согласно табл. 3.8.1. Значение А6 определяет дальнейшие процессы в схеме параллельного опроса. Анализ проводится одновременно во всех ИВУ

k

, на которые поступили сигналы запросов ЗПрк.

Младшие разряды кодов ВУ анализируются аналогично. После параллельного анализа всех разрядов кодов на ШД будет выведен код К7…К0 внешнего устройства, обладающего самым высоким приоритетом. После обслуживания запроса этого устройства происходит сброс всех триггеров запроса.

Способ «дейзи–цепочки»

(

daisy

chain

). Рассмотрим этот способ для случая, когда используются три источника запросов на прерывания, сигналы ЗПр1…3ПрЗ которых фиксируются в триггерах Т1…ТЗ (рис. 3.8.4). «Дейзи–цепочка» составлена из шести логических элементов ЛЭ 1…6, причем ЛЭ 6 следует задействовать при увеличении источников прерывания.

Если, хотя бы в одном из триггеров Т1…ТЗ, зафиксирован запрос на прерывание ЗПр1…3ПрЗ, то в ЦП поступит сигнал запроса (на схеме не показано). В ответ процессор выдает сигнал подтверждение запроса ПЗ = 1, который отпирает элемент ЛЭ 1. Если сигнал запроса был зафиксирован триггером Т1, его выходной сигнал

Q

1 = 1. В этом случае на выходе ЛЭ 1 сигнал подтверждения запроса П31 = 1, а на выходе ЛЭ 2 сигнал будет равен нулю. Поэтому сигналы П32 = ПЗЗ = 0.

При отсутствии запроса ЗПр1 (

Q

1 = 0) сигнал П31 = 0, на выходе ЛЭ 2 сигнал равен 1 и ЛЭ 3 открыт. Поэтому для сигнала ЗПр2 открыт путь на вход ЛЭ 3. Таким образом, сигнал подтверждения запроса ПЗ с выхода ЦП распространяется от одного триггера к другому пока не будет заблокирован первым встретившимся на пути триггером Т

k

, который принял запрос на прерывание ЗПр

k

. Выходной сигнал этого триггера

Qk

= ПЗ

k

= 1. Он может быть использован для формирования вектора прерывания внешнего устройства ВУ

k

, пославшего запрос. При сигнале ПЗ = 0 все прерывания будут заблокированы.

Маскирование прерываний.

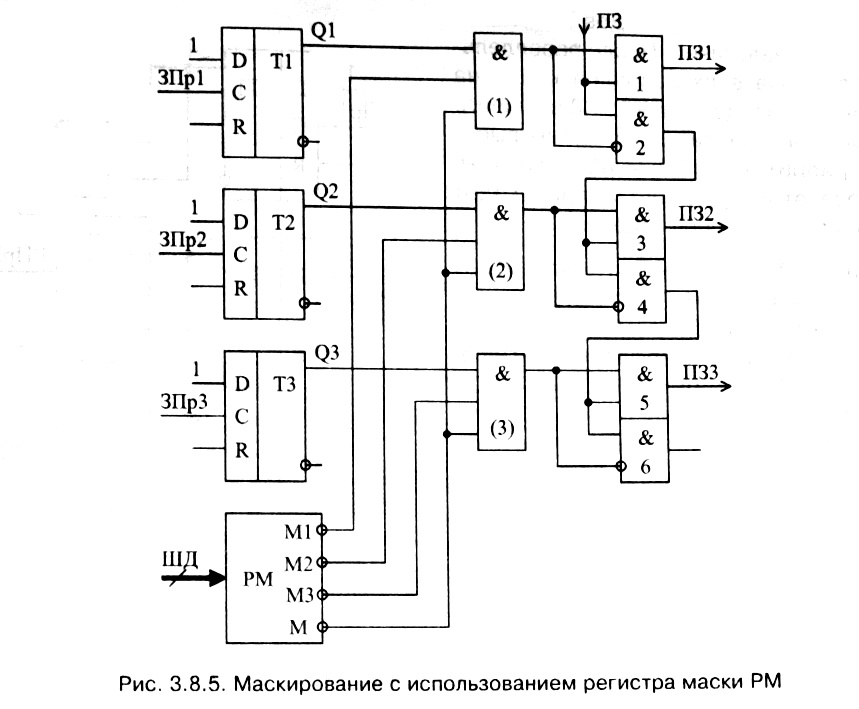

Маскирование с использованием регистров. Источники прерываний, расположенные в конце опросного списка игнорируются из–за своего низкого приоритета и при длительном обслуживании прерываний с более высокими приоритетами могут оказаться вообще не обслуженными. Одной из мер обслуживания прерываний низкого уровня является отключение источников прерываний в начале списка опроса или отключение всей системы прерываний. Для этих целей в системах прерываний используются регистры разрешения прерываний РРП, или регистры маскирования (РМ), которые позволяют разрешать/запрещать (маскировать) любые запросы на прерывания системы.

На рис. 3.8.5 приведена схема, иллюстрирующая принцип маскирования прерываний. Если программно в РРП записать ?М1 = 0, то запрос ЗПр1 будет маскирован (элемент 1 заперт) и источник с запросом ЗПр2, имеющим меньший приоритет, получит разрешение на обслуживание прерывания. При ?М1 = 0 запрещено обслуживание всех прерываний.

Как показано выше, при использовании «дейзи–цепочки» более высоким приоритетом обладают первые звенья цепочки. С помощью регистра разрешения прерывания РРП можно разрешить прерывания для последующих звеньев цепочки (рис. 3.8.5). Действительно, установкой в РРП бита ?М1 =0 маскируется действие запроса ЗПр1, установкой битов ?М1 = ?М2 = 0 блокируются запросы ЗПр1, ЗПр2 и т. д.

Маскирование с использованием компаратора.

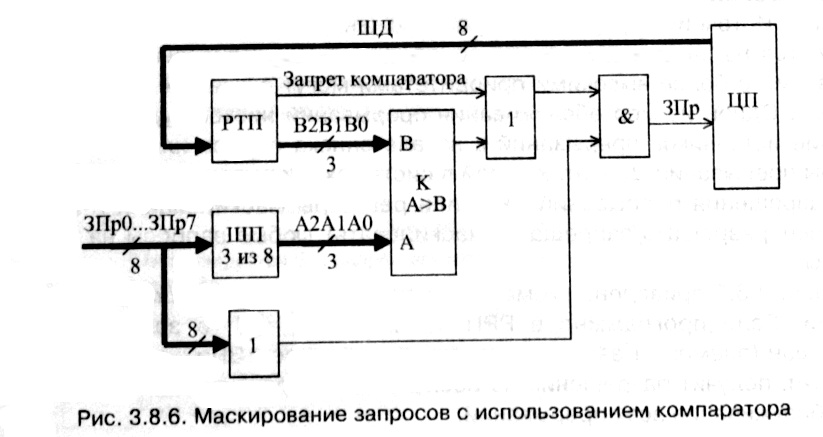

Еще один способ принятия решения о разрешении или запрещении прерывания состоит в том, чтобы исключить все прерывания с приоритетом, не превосходящим приоритет прерывания, принятого на обработку. На рис. 3.8.6 приведен пример реализации такого подхода с использованием цифрового компаратора.

Устройство помимо логических элементов содержит:

? четырехразрядный регистр текущего приоритета РТП, в который заносится код В2В1В0 обслуживаемого ВУ, а также бит разрешения/запрета работы компаратора;

? шифратор приоритетов ШП 3 из 8, позволяющий из поступивших на вход запросов выделить запрос А2А1А0 с наивысшим приоритетом;

? компаратор К, вырабатывающий единичный выходной сигнал при условии А2А1А0> В2В1В0.

В приведенной на рис. 3.8.6 схеме исключается прием прерывания с приоритетом меньшим или равным приоритету прерывания, принятого на обработку. Это предотвращает приостановку программы обработки прерывания при поступлении повторного запроса на прерывание от того же самого источника прерываний. Для возможности обслуживания запроса с самым низким уровнем приоритета в четвертый разряд («Запрет компаратора») РТП должна быть занесена единица. В этом случае любой из сигналов запроса ЗПр0…ЗПр7 получает доступ к входу запросов на прерывания ЦП.

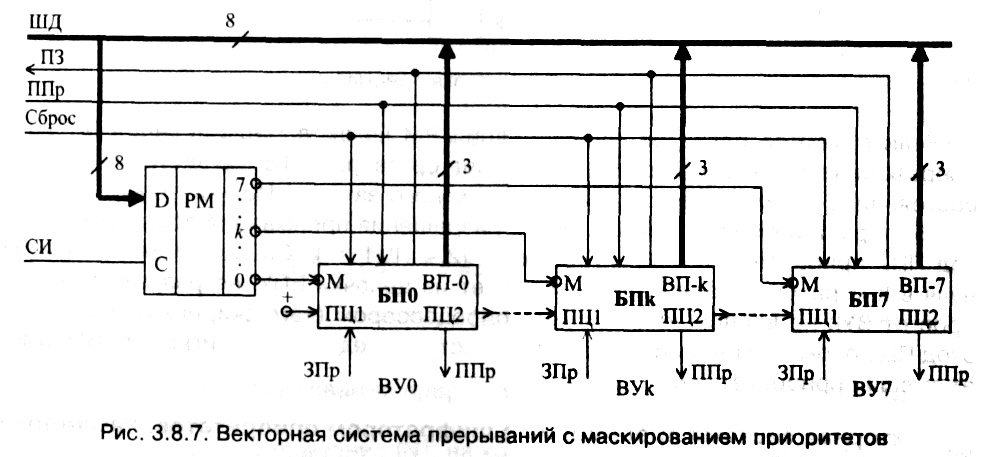

Векторная система прерываний с маскированием приоритетов.

В качестве примера рассмотрим устройство приоритетных прерываний для обслуживания восьми ВУ (рис. 3.8.7). В его состав входят:

? восемь блоков прерывания БП

k

(рис. 3.8.8), с помощью которых осуществляется связь выбранного ВУ

k

(

k

= 0, …, 7) с микропроцессором;

? восьмиразрядный регистр маски РМ, предназначенный для маскирования (блокирования) входов запроса прерываний (ЗПр) внешних устройств. Приоритет ВУ определяется закрепленным за ним номером.

Рассмотрим работу устройства. Пусть на входе приоритетной цепи ПЦ1 блока прерывания БП

k

установлен разрешающий сигнал ПЦ1 = 1, а на входе маскирования — запрещающий сигнал ?М = 1 (т. е. маскирование отсутствует). Тогда с поступлением от ВУк сигнала запроса на прерывание (ЗПр = 1) триггер запроса (ТЗ) перейдет в единичное состояние. При этом:

? на его прямом выходе формируется сигнал приоритетного запроса ПЗ = 1, который передается на вход запроса прерывания микропроцессора;

? сигналом с инверсного выхода ТЗ закрывается схема совпадения 5, не пропуская на выход блока прерывания БП

k

разрешающий сигнал ПЦ1 = 1. Поэтому ПЦ2 = 0 и для внешних устройств с более высокими номерами к прерывания запрещены;

? готовятся цепи для сброса ТЗ и запуска триггера активности ТА. При поступлении ответного сигнала подтверждения прерывания ППр = 0 сбрасывается в нулевое состояние ТЗ и устанавливается в единичное состояние ТА. Сигналом с выхода ТА:

? открываются схемы совпадения 6–8, через которые передается аппаратно установленный (например, путем распайки к источнику напряжения и корпусу) трехразрядный код вектора прерывания ВП2ВП1ВП0 или однобайтная команда

RST

, запускающая подпрограмму обслуживания прерывания;

? подтверждается запрос прерывания ПЗПр = 1, т. е. указывается ВУ

k

на начало его обслуживания.

Если с выхода регистра маскирования РМ на вход маскирования М блока прерываний БП

k

поступает М = 0, то триггер запроса ТЗ находится в нулевом состоянии. В этом случае сигнал приоритетного запроса ПЗ =0, схема совпадения 5 открыта и входной сигнал ПЦ = 1 разрешения прерывания поступает на выход ПЦ2 приоритетной цепи БП

k

, т. е. ПЦ2 = ПЦ1 = 1. Следовательно, наличие нуля в

k

–м разряде кода маски исключает из цепочки БП

k

, не разрывая ее. Запрос от ВУ

k

не воспринимается микропроцессором (замаскирован). Так как на вход ПЦ1 блока прерываний БП0 всегда поступает единичный сигнал, то ВУ0 имеет высший приоритет, а ВУ7 — низший.

Векторная система прерываний с шифратором приоритетов.

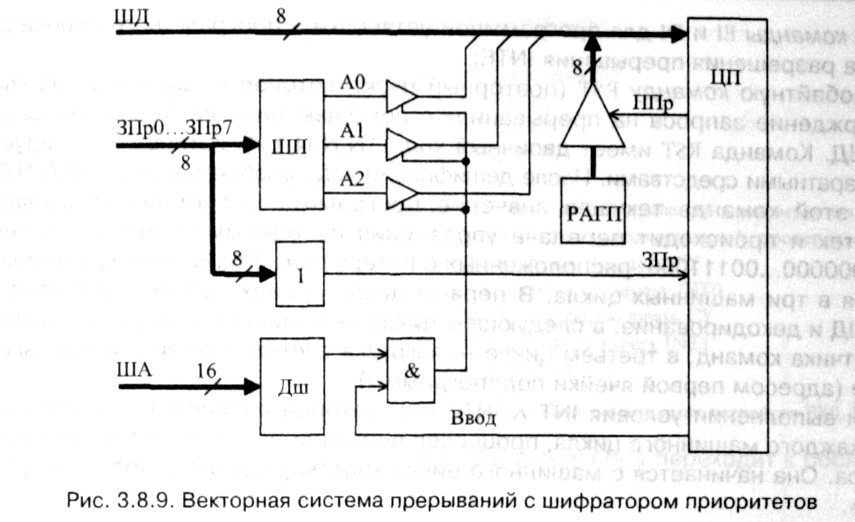

Рассмотрим схему на рис. 3.8.9, содержащую:

? шифратор приоритетов

ШП 3 из 8, предназначенный для определения максимального номера к поступившего на его вход запроса на прерывание ЗПр

k

(

k

= 0…7). Внешнее устройство ВУ

k

с максимальным к обладает наивысшим приоритетом;

? три управляемых буфера, подключенные к выходам шифратора ШП. Они служат для ввода кода выбранного ВУ в ЦП;

? дешифратор адреса

(Дш), позволяющий обратится к данной схеме;

? регистр адреса главной программы

(РАГП) обработки прерываний с управляемым буфером для считывания адреса. Отметим, что фиксированный адрес главной программы может быть задан путем распайки входных линий буфера к корпусу или полюсу источника питания.

Запросы ЗПр0…ЗПр7, поступающие от ВУ на входы шифратора приоритетов и элемента ИЛИ, формируют (не зависимо от их числа):

? на выходах шифратора приоритета трехразрядный двоичный код А2А1

A

0

, значение которого в десятичном исчислении соответствует максимальному номеру к запроса ЗПрк или ВУк;

? на входе ЦП сигнал запроса на прерывание ЗПр.

В ответ на запрос ЦП выдает сигнал подтверждения прерывания ППр. С помощью этого сигнала фиксированный начальный адрес главной программы прерываний из РАГП по ШД поступает в ЦП. Начинается исполнение главной программы. Прежде всего, командой «Ввод» открываются буферы для передачи кода выбранного ВУ в ЦП. Этот код может быть использован для перехода на подпрограмму обслуживания выбранного ВУ. В том случае, когда ВУ являются однотипными и допускают совместное обслуживание, может быть вызвана общая подпрограмма обслуживания.

onetwoclick.ru

onetwoclick.ru