- Основные функции и состав процессора

- Из чего состоит процессор

- Состав восьмиразрядного процессора

- Блок десятичной коррекции

- Регистр признаков

- Регистры процессора

- Указатель команд, или программный счетчик ( Program Counter — PC).

- Указатель стека

- Блок управления

- Интерфейс микропроцессора

- Состав шестнадцатиразрядного микропроцессора

- Назначение управляющих сигналов

- Принцип формирования адресов

- О сопроцессорах

- Внутренние ресурсы процессора

Основные функции и состав процессора

Основные функции и состав процессора

На процессор возлагается выполнение операций, предусмотренных его системой команд.

При выполнении программы центральный процессор микропроцессорной системы обеспечивает выполнение всех функций, предусмотренных программной. К ним относится:

- формирование адреса команд или данных, хранящихся оперативной памяти;

- выборка команд из памяти и их дешифрация;

- прием данных из оперативной памяти, выполнение над ними арифметических, логических и других операций, определяемых кодом команды, и передача обработанных данных во внешние устройства или память;

- формирование сигналов состояния, управления и времени, необходимых для нормальной работы внутренних узлов, а также внешних устройств и памяти;

- временное хранение результатов выполненных операций, адресов, формируемых сигналов состояния и других данных;

- прием сигналов запроса от внешних устройств и их обслуживание.

Из чего состоит процессор

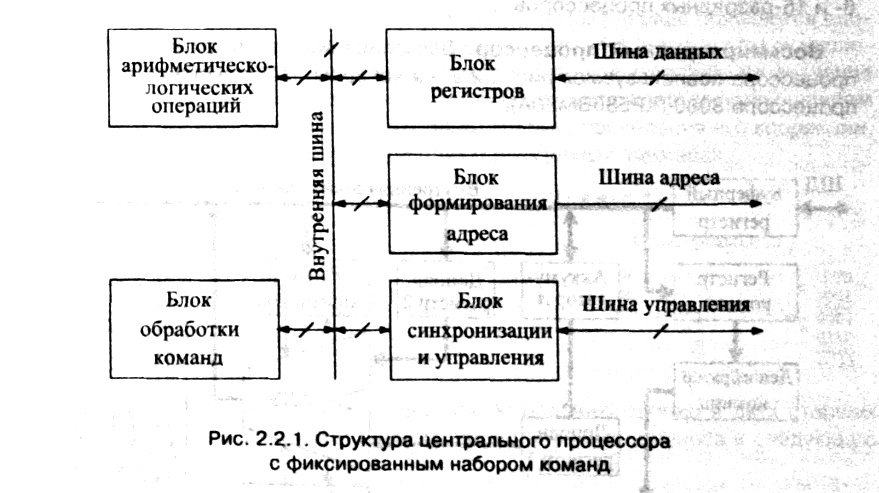

Для выполнения перечисленных функций процессор должен располагать необходимым набором аппаратных средств. Основными функциональными блоками процессора являются (рис. 2.2.1):

- блок арифметическо–логических операций, выполняющий обработку поступающих данных. Перечень выполняемых операций зависит от типа микропроцессора. В большинстве процессоров выполняются следующие операции: арифметическое сложение и вычитание; логические операции ИЛИ, И, НЕ, исключающее ИЛИ; операции инкремента и декремента; логические и арифметические сдвиги вправо и влево. Что касается операций умножения и деления, то в 8–разрядных процессорах они выполняются программным способом, в 16–разрядных процессорах для их реализации предусмотрены специальные команды. Блок арифметическо–логических операций строится на основе двоичного сумматора со схемами ускоренного переноса, регистров для временного хранения операндов и регистров–сдвигателей, комбинационных схем для выработки логических условий, схем десятичной коррекции и других функциональных узлов;

- блок обработки команд, предназначенный для приема и декодирования команд, а также для формирования сигналов управления узлами обработки денных;

- блок формирования адресов, обеспечивающий адресацию к внешней памяти и внешним устройствам. Его основными узлами являются программный счетчик, указатель стека, инкрементор–декрементор, адресный регистр;

- блок регистров, выполняющих функции сверхоперативной внутренней памяти, функции временного хранения операндов и др.;

- блок синхронизации и управления, координирующий работу всех узлов процессора;

- внутренняя шина, которая используется для связи между отдельными блоками и узлами процессора. В общем случае она включает в себя шины для передачи данных, адреса и управляющих сигналов.

В качестве примеров рассмотрим структурно–функциональную организацию 8– и 16–разрядных процессоров.

Состав восьмиразрядного процессора

Для описания основных узлов 8–разрядного процессора воспользуемся рис. 2.2.2, на котором изображена структурная схема процессора 8080 (КР580ВМ80А).

Арифметическо–логическое устройство (АЛУ) позволяет выполнить следующие операции над 8–разрядными операндами:

- арифметическое сложение двух операндов с передачей переноса в старший разряд (и без него) и вычитание с передачей заема в младший разряд (и без него);

- логическое сложение, умножение, исключающее ИЛИ и сравнение;

- четыре вида циклических сдвигов;

- арифметические операции над десятичными числами.

При выполнении операций один из операндов поступает в АЛУ через аккумулятор А и дополнительный регистр 1, другой операнд — через дополнительный регистр 2. Циклические сдвиги выполняются только над содержимым аккумулятора А. В аккумулятор также помещаются результаты выполненных в АЛУ операций.

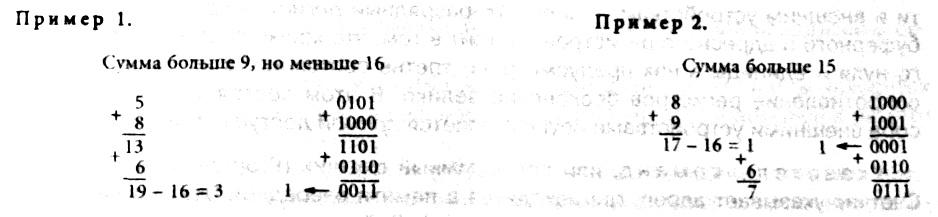

Блок десятичной коррекции

При суммировании десятичных чисел может потребоваться коррекция результата, для выполнения которой в микропроцессоре предусмотрен блок десятичной коррекции. При сложении каждый разряд десятичного числа (цифра) представляется четырехразрядным двоичным кодом (полубайтом, тетрадой), например, кодом 8421. Сложение полубайтов происходит по правилам двоичной арифметики. Если сумма больше 9, то возникает необходимость в проведении коррекции. Коррекция осуществляется дополнительным прибавлением двоичного числа 0110 (6) к полученному результату. Это обусловлено тем, что вес пятого разряда двоичного числа составляет 16 десятичных единиц, а вес старшего разряда десятичного числа — 10, т.е. разность равна 6.

Если при сложении получен результат 10… 15, то прибавление числа 6 (0110)2 приведет к появлению 1 в пятом разряде полубайта. Этот разряд «уходит» в старший полубайт и забирает с собой «добавку» (6), оставляя правильный результат. В том случае, когда результат 16… 18, в пятом разряде появляется единица, значение которой (до переноса) соответствует 16 в десятичном исчислении. После переноса единицы пятого разряда в старший полубайт ее значение становится равным 10. Таким образом, перенос сопровождается уменьшением результата на 6 десятичных единиц, что также требует проведения его коррекции. Принцип коррекции иллюстрируется на двух приведенных примерах.

Неправильный результат обнаруживается по наличию единиц в двух старших разрядах (3–й и 2–й), в третьем и первом или по наличию переноса в следующую тетраду.

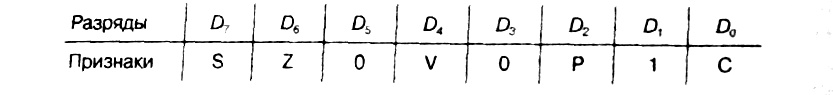

Регистр признаков

АЛУ непосредственно связано с 5–разрядным регистром признаков (флагов), в котором фиксируется результат выполнения некоторых арифметических и логических операций. Регистр содержит пять триггеров:

- триггер переноса, вырабатывающий сигнал С = 1, если при выполнении операций сложения и сдвига появляется единица переноса из старшего разряда;

- триггер дополнительного переноса, вырабатывающий сигнал V = 1, если при выполнении операции с двоично–десятичными кодами появляется единица из третьего разряда (старшего разряда младшего полубайта);

- триггер нуля, вырабатывающий сигнал Z = 1, если результат операции равен нулю;

- триггер знака, вырабатывающий сигнал S = 1, если значение старшего разряда операнда (в дополнительном коде) равно единице, т. е. результат операции — отрицательное число;

- триггер четности, вырабатывающий сигнал Р = 1, если результат операции содержит четное число единиц.

Указанные триггеры обеспечивают выполнение в программе условных переходов. Например, если результат выполнения предыдущей операции равен нулю, то триггер нуля устанавливается в единичное состояние (Z = 1), и условие перехода в другую часть программы окажется выполненным. Распределение разрядов регистра признаков условий в байте при передаче по шине данных следующее:

Регистры процессора

Доступ к регистрам, в том числе к счетчику команд и указателю стека, осуществляется через мультиплексоры с помощью селектора регистров.

Регистры общего назначения (РОН) играют роль аккумуляторов, когда в них содержатся обрабатываемые данные, либо указателей, когда в них хранятся адреса операндов. Регистры В, С, D, Е, Н, L могут быть использованы в программе как отдельные 8–разрядные регистры или как 16–разрядные регистровые пары ВС, DE, HL. Название пары В, D, Н всегда соответствует названию первого регистра пары, в котором хранится старший байт 16–разрядного числа. 16–разрядный регистр Н служит адресным регистром: при косвенной регистровой адресации он хранит исполнительный адрес, поступающий из основной памяти.

Регистры W и Z не являются программно доступными и используются для выполнения команд внутри микропроцессора. В них хранятся второй и третий байт команды.

Обмен информацией между микропроцессором и внешними устройствами осуществляется через двунаправленный буферный регистр, а адресация к памяти и внешним устройствам — через 16–разрядный регистр адреса. Особенность буферного и адресного регистров состоит в том, что кроме состояния логического нуля и единицы в них предусмотрено третье состояние, в котором выходное сопротивление регистров бесконечно велико. В этом состоянии микропроцессора внешними устройствами осуществляется прямой доступ к памяти.

Указатель команд, или программный счетчик ( Program Counter — PC).

Счетчик указывает адрес, где находится в памяти очередной байт команды (для команд используются 3–байтовые форматы). Байты команд обычно выбираются в порядке нарастания их адресов. Поэтому после выборки каждого очередного байта схема инкремента–декремента увеличивает содержимое программного счетчика на единицу. Перед началом выборки какой–нибудь команды в счетчик заносится адрес ее первого байта. В процессе выбора 3–байтной команды содержимое счетчика увеличивается трижды. Обычный порядок следования адресов может быть изменен. Для этого в счетчике предусмотрена возможность записи начального адреса той части программы, именуемой подпрограммой, которая должна выполниться.

Указатель стека

Указатель стека (StackPointer —SP) представляет собой 16–разрядный регистр, предназначенный для быстрой адресации особого вида памяти, и именуемой стеком. Стековая память используется при обслуживании прерываний и характеризуется тем, что из нее первыми выбираются данные, которые поступили последними.

В стек заносится адрес возврата к прерванной программе на время обработки микропроцессором подпрограммы, содержимое аккумулятора, регистра признаков.

Блок управления

Первый байт исполняемой команды записывается в регистр команд. В дешифраторе команд формируются сигналы, под действием которых в устройстве управления запускается микропрограмма для выполнения требуемой операции. Микропрограммы операций, определяемых набором команд микропроцессора, «зашиты» в управляющую память. На входы устройства управления поступают:

- две неперекрывающиеся последовательности тактовых импульсов (Ф1, Ф2) с периодом Т;

- сигнал готовности (READY) внешних устройств и памяти к обмену информацией с микропроцессором;

- сигнал запроса от внешних устройств на прерывание (INT) выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания;

- сигнал запроса от внешних устройств на захват шин (HOLD), как правило, для организации обмена информацией по каналу прямого доступа к памяти;

- сигнал сброса (RESET), по которому происходит начальная установка микропроцессора.

С выхода устройства управления снимаются сигналы для управления внутренними узлами (на рис. 2.2.3 эти связи не показаны) процессора и внешними устройствами.

Для управления внешними устройствами вырабатываются:

- сигнал синхронизации (SYNC), указывающий на начало каждого машинного цикла — промежутка времени, необходимого для одного обращения процессора к внешним устройствам или памяти;

- сигнал приема (DBIN), указывающий на готовность процессора к приему данных;

- сигнал ожидания (WAIT), указывающий на то, что процессор находится в состоянии ожидания;

- сигнал подтверждения захвата (HLDA), подтверждающий, что шины находятся в высокоомном состоянии, и внешние устройства могут обращаться к памяти напрямую, минуя процессор;

- сигнал разрешения прерывания(INTE), свидетельствующий о том, что триггер разрешения прерывания в блоке управления находится в состоянии логической единицы, при котором возможен прием сигналов запроса;

- сигнал ?Выдача(?WR= 0), указывающий на то, что процессор выдал информацию на шину данных для ее записи в память или передачи во внешние устройства.

Интерфейс микропроцессора

Обмен информацией между узлами процессора осуществляется по 8–разрядной внутренней шине данных, а с внешней 8–разрядной шиной данных ШД — через буферный регистр. Для адресации к памяти и внешним устройствам используются 16–разрядная шина адреса ША и регистр адреса.

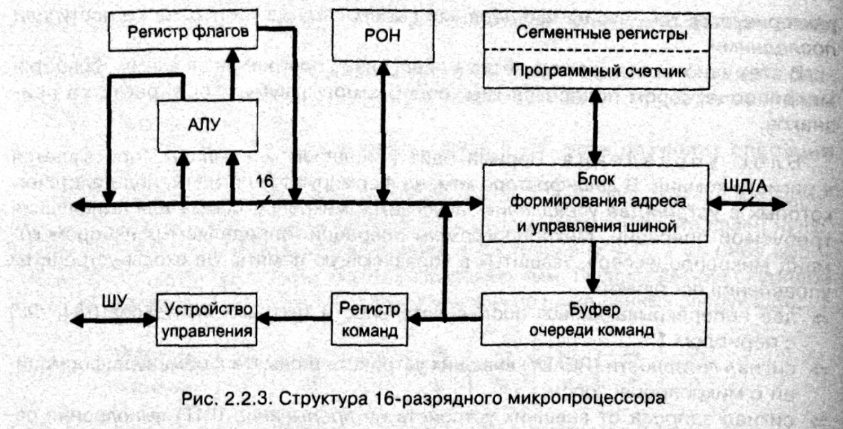

Состав шестнадцатиразрядного микропроцессора

Структурная схема 16–разрядного процессора (8086) изображена на рис. 2.2.3.

Микропроцессор содержит:

- арифметическо–логическое устройство (АЛУ) со стандартным набором операций;

- регистр флагов или регистр слова состояния, отражающий состояние процессора после выполнения каждой команды. Например, флаг Z фиксирует нулевой результат операции АЛУ;

- восемь 16–разрядных регистров общего назначения (РОН), предназначенных для хранения адресов/данных: АХ (АН, AL), DX ( DН, DL), СХ (СН, CL), ВХ (ВН, BL), BP, SP DI, SI;

- блок формирования адреса и управления шиной, обеспечивающий формирование адреса путем суммирования содержимого одного из индексных регистров (DI, SI) с адресом из памяти, временное мультиплексирование шины данных/адреса (ШД/А), автоматическое заполнение буфера очереди команд следующими командами. Блок формирования адреса и управления шиной содержит буферный регистр, сумматор и логику управления шиной;

- регистр команд, предназначенный для приема команды из внешней памяти;

- устройство управления, обеспечивающее синхронизацию процессора, управление машинными циклами и захватом шины, обслуживание запросов на прерывание от внешних устройств;

- буфер очереди команд, позволяющий хранить до шести байт принимаемой команды;

- четыре 16–разрядных сегментных регистра (CS, SS, DS, ES) и программный счетчик (Instruction Pointer — IP), принимающие участие в формировании адреса.

Назначение управляющих сигналов

Управляющие сигналы поступают по шине управления ШУ (рис. 2.2.3) микропроцессора (МП), который работает в двух режимах: минимальной и максимальной конфигурации. Сигналы, используемые в обоих режимах:

- CLK – Тактовые импульсы, предназначенные для синхронизации МП

- RESET – Сброс МП в начальное состояние

- READY Сигнал готовности ВУ, опрашиваемый МП в третьем такте каждого машинного цикла

- NMI Сигнал немаскируемых запросов

- INTR Сигнал маскируемых векторных запросов. Маской служит флаг разрешения прерывания

- IF A16/S3…A19/S6 А16…А19 — старшие разряды адресов при обращениях к памяти.

- S4 S3 — код сегментных регистров (00 —ES; 01 —SS; 10 —CS, ВВ или прерывание; 11 —DS).

- S5 — сигнал для индицирования флага прерывания IF; обновляется в начале каждого такта.

S6 = 0 при S5 =IF = 1 BHE#/S7 ВНЕ# = 0 подается на старший Н–банк при обращениях к памяти.

S7— сигнал о состоянии процессора, где # — знак инверсии RD# Чтение памяти и порта (в режиме минимальной конфигурации)

TEST# Вывод микросхемы, опрашиваемый командой

WAIT#: при TEST = 1 — режим опроса через 5 тактов; при TEST = 0 — режим ожидания MN/

MX# Переключение режимов минимальной/максимальной конфигурации

В режиме минимальной конфигурации ( MN/ MX = 1) МП вырабатывает следующие управляющие сигналы:

ALE Строб адреса при записи его во внешний буферный регистр

М/IO# Выбор обмена память/порт ВВ

DT/R# Выбор направления обмена или режима записи/чтения

WR# Запись (по фронту) в память или порт ВВ

DEN# Разрешение передачи данных через шину данных

HOLD, HLDA Сигналы запроса на захват шины и подтверждения захвата при прямом доступе к памяти

Сигналы для режима максимальной конфигурации (MN/MX = 0): S2# S1#

S0# Код состояния или типа цикла МП: 000 — подтверждение прерывания; 001 — чтение порта ВВ; 010 — запись в порт ВВ; 011 — останов; 100 — выборка команды; 101 — чтение памяти; 111 — пассивное состояние QS1

QS0 Код состояния очереди: 00 — пассивное состояние (нет операции); 01 — очистка очереди; 10 — выборка первого байта команды; 11 — выборка следующего байта команды RQ/GT1,RQ/GT0

Сигналы запроса на захват шины, разрешения захвата при прямом доступе к памяти и освобождения шины

При обозначении сигналов использован символ #, означающий инверсию, т.е. А# = А.

Рассмотрим несколько подробнее организацию очереди команд и принцип формирования адресов с помощью сегментных регистров.

Организация очереди команд при выполнении программы значительное время расходуется на выборку команд из памяти. Поэтому блок формирования адреса и управления шиной старается поддерживать заполненным буфер очереди команд, считывая из памяти последующие команды во время выполнения текущей команды, когда ШД/А остается свободной.

После завершения текущей команды следующая команда считывается из буфера. Так как не требуется обращения к памяти, повышается быстродействие процессора. При выполнения команд условных и безусловных переходов, связанных с передачей управления другой ячейке памяти, происходит очистка буфера, после чего он начинает заполняться вновь.

Принцип формирования адресов

Поставим задачу сформировать 20–разрядный адрес (addr20), обеспечивающий доступ к 220 = 1М байт памяти, с помощью двух 16–разрядных регистров. Каждый из 16–разрядных регистров обеспечивает доступ к 216 ячейкам или к 64К байт памяти. Поэтому выделим в 1М байт памяти сегмент емкостью 64К байт с условием, чтобы младший разряд его шестнадцатеричного кода начального адреса был равен нулю, т. е. код адреса имел вид ХХХХ0

h, где X = 0 или 1, h — обозначение 16–ричного кода (hexadecimal). Один из регистров выберем в качестве селектора сегмента(sel), другой — в качестве регистра смещения (offset). Представим адрес в виде суммы addr20 = 1 6 x sel +offset =XXXX0h +YYYYh.

Из выражения следует, что путем изменения содержимого селектора (ХХХХ h) и регистра смещения (YYYYh) от 0000 h до FFFFh, можно получить 164х164 комбинаций адресов. Однако среди них имеются одинаковые коды. Общее число ячеек памяти с различными адресами составляет 220 – 24 + 216.

На рис. 2.2.4, а показано, как можно обеспечить доступ к памяти с числом ячеек 220 (или емкостью 1 M байт при использовании однобайтных ячеек).

В качестве селектора, который можно рассматривать как указатель сегмента, в процессорах используются сегментные регистры (регистры кода CS, стека SS, данных DS и дополнительный регистр ES), а в качестве регистров смещения — регистры общего назначения (программный счетчик IP, указатель стека SP, указатель базы BP и регистры автоинкрементной SI и автодекрементной DI адресации). Возможны следующие пары регистров:

CS <—>IP,

SS <—>SP,

DS <—>BP,

DS <—>SI,

ES <—>DI. На рис. 2.2.4, б показана в качестве примера реализация принципа адресации с использованием пары

SS <—>SP.

О сопроцессорах

Для расширения функциональных возможностей и повышения производительности центрального процессора микропроцессорная система может содержать дополнительные процессоры, или сопроцессоры. Например, в первых поколениях компьютеров для расширения функций центрального процессора 80286 использовался сопроцессор 80287.

Сопроцессор 80287 предназначен для выполнения операций над числами с плавающей точкой (запятой), которые потребовали бы от основного процессора больших затрат машинного времени. Поэтому такой сопроцессор называют числовым процессором, процессором для обработки числовых данных, процессором

NDP (Numeric Data Processor) или математическим сопроцессором. Сопроцессор выполняет такие сложные операции, как деление длинных операндов, вычисление тригонометрических функций, извлечение квадратного корня и нахождение логарифма в 10–100 раз быстрее основного процессора. Точность результатов расчетов значительно выше точности, обеспечиваемой вычислительными модулями, входящими в состав самих процессоров. Выигрыш реализуется только при выполнении программ, написанных с учетом на совместное использование сопроцессора с основным процессором. При совместной работе операции сложения, вычитания и умножения выполняются основным процессором и не передаются сопроцессору.

Сопроцессор имеет собственную систему команд (инструкций), которая отличается от системы команд процессора. Выполняемая программа должна сама определять наличие сопроцессора и после этого использовать написанные для него инструкции. Большинство программ, рассчитанных на использование сопроцессоров, обнаруживают его присутствие и используют предоставляемые возможности.

Наиболее эффективно сопроцессоры используются в программах со сложными математическими расчетами: в электронных таблицах, базах данных, статистических программах и системах автоматизированного проектирования. При работе с текстовыми редакторами сопроцессор не используется.

В процессорах 80486 и более поздних моделях используются встроенные сопроцессоры. Они выполняются в виде устройства с плавающей точкой (Floating Point Unit — FPU), входящего в состав процессора, и располагаются на том же кристалле. Инструкции над числами с плавающей точкой входят в систему команд процессора.

Внутренние ресурсы процессора

К ним относятся:

- типы данных, которые процессор способен распознавать и обрабатывать, т. е. выполнять над ними различные действия и операции;

- программно–доступные регистры, предназначенные для хранения данных и адресов в процессе выполнения программы;

- режимы адресации (Addressing Mode), или реализуемые процессором способы адресации. Под способом адресации будем понимать меток определения или вычисления так называемого эффективного адреса ( Effective Address — ЕА), обеспечивающего доступ к операндам или передачу управления. Внутренние ресурсы встроены в процессор и отражены в его системе команд и поэтому используются не только при программировании прикладных задач, но и при непосредственном исполнении программы.

Архитектура процессоров предоставляет наиболее часто требуемые типы данных, регистры и режимы адресации. Каждый процессор поддерживает несколько типов данных, режимов адресации и содержит определенный набор внутренних регистров.

Разнообразие, доступность и умелое использование ресурсов способствует повышению производительности системы. Недостающие или отсутствующие ресурсы допускают программное моделирование, но снижают производительность.

Для разработки системной программы используются жестко связанные с архитектурой процессора системные ресурсы, к которым относят адреса памяти и ввода/вывода, запросы прерываний и каналы прямого доступа к памяти. Они обеспечивают управление виртуальной памятью, мультизадачностью и средствами защиты. Системные ресурсы образуют основу возможностей защищенного режима.

onetwoclick.ru

onetwoclick.ru