Архитектура микропроцессоров.

Архитектура микропроцессоров.

Эта глава посвящена архитектурным особенностям микропроцессоров. В ней приведены общие сведения о микропроцессорах, рассматриваются принципы структурно – функциональной организации) типы данных, регистровая память, способы адресации и система команд микропроцессоров. Излагаемый материал иллюстрируется на простейших 8– и 16–разрядных процессорах.

Основные понятия

Микропроцессор — это программно–управляемое устройство в виде интегральной микросхемы (БИС или СБИС), предназначенное для обработки цифровой информации. Поскольку все современные микропроцессоры имеют интегральное исполнение, синонимом микропроцессора стал термин процессор.

Микроконтроллер— это специализированный процессор, предназначенный для реализации функций управления (control— управление).

{xtypo_quote}Цифровой сигнальный процессор(Digital Signal Processor — DSP) — это специализированный процессор, предназначенный для обработки цифровых сигналов. {/xtypo_quote}

Микропроцессорная система представляет собой функционально законченное изделие, состоящее из нескольких цифровых устройств, включая процессор. Это понятие объединяет широкий набор законченных изделий, начиная с микроконтроллеров, выполненных на интегральных микросхемах, и кончая компьютерными системами, представляющими собой набор отдельных конструктивно оформленных устройств (системный блок, клавиатура, монитор и др.). В дальнейшем рассматриваются простейшие (однокристальные) микропроцессорные системы, содержащие помимо процессора основную память и устройства ввода/вывода. Такие микропроцессорные системы можно отнести к классу микропроцессоров.

Под организацией процессора понимают совокупность его узлов (устройств, блоков, модулей), связи между узлами и их функциональные характеристики. Организация определяет аппаратную организацию процессора, т. е. состав и взаимодействие его аппаратных средств. Выделяют два уровня организации:

? физическую организацию в виде принципиальной схемы;

? логическую организацию в виде структурно–функциональной схемы.

В дальнейшем рассматривается организация микропроцессоров на логическом уровне, или структурно–функциональная организация процессоров.

Под архитектурой процессора будем понимать совокупность его программно–аппаратных средств, обеспечивающих обработку цифровой информации (выполнение программы), т. е. совокупность всех средств, доступных программе (или пользователю). Это более общее понятие по сравнению с понятием организация включает в себя набор программно–доступных регистров и операционных устройств, систему основных команд и способов адресации, объем и организацию адресуемой памяти, виды и способы обработки данных (обмен, прерывания, примой доступ к памяти и др.).

{xtypo_quote}Например, современные 32–разрядные процессоры х86 с архитектурой IA–32 (Intel Architecture — 2 bit ) имеют стандартный набор регистров, общую систему основных команд, одинаковые способы организации и адресации памяти, защиты памяти и обслуживания прерываний. Отметим, что понятие архитектуры в большей степени характеризует свойства системы, чем устройства. {/xtypo_quote}

Основные виды архитектур

По форматам используемых команд (инструкций) можно выделить:

? CISC–архитектуру, которая относится к процессорам (компьютерам) с полным набором команд (Complete Instruction Set Computer— CISC). Она реализована во многих типах микропроцессоров (например Pentium), выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации.

Система команд процессоров с CISC–архитектурой может содержать несколько сотен команд разного формата (от 1 до 15 байт), или степени сложности, и использовать более 10 различных способов адресации, что позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач.

Развитие традиционных CISC

Архитектур микропроцессоров по пути расширения функциональных возможностей и снижения затрат на программирование привело к увеличению числа команд в наборе и числа микрокоманд в команде. Следствием этого явилось усложнение интегральных схем и снижение быстродействия выполнения программ. Один из возможных путей устранения указанных недостатков состоит в использовании сокращенного набора команд, организация которого подчинена увеличению скоростей их выполнения;

? RISC–архитектуру, которая относится к процессорам (компьютерам) с сокращенным набором команд (Reduced instruction Set Computer — RISC). Появление RISC –архитектуры продиктовано тем, что многие CISC –команды и способы адресации используются достаточно редко. Основная особенность RISC–архитектуры проявляется в том, что система команд состоит из небольшого количества часто используемых команд одинакового формата, которые могут быть выполнены за один командный цикл (такт) центрального процессора. Более сложные, редко используемые команды реализуются на программном уровне. Однако за счет значительного повышения скорости исполнения команд средняя производительность RISC–процессоров может оказаться выше, чем у процессоров с CISC–архитектурой.

{xtypo_quote}Большинство команд RISC –процессоров связано с операцией регистр–регистр. Для обращения к памяти оставлены наиболее простые с точки зрения временных затрат операции загрузки в регистры и записи в память. {/xtypo_quote}

Современные RISC –процессоры реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта, и используют небольшое число наиболее простых способов адресации (регистровую, индексную и некоторые другие).

Для сокращения количества обращений к внешней оперативной памяти RISC –процессоры содержат десятки–сотни регистров общего назначения (РОН), тогда как в CISC–процессорах всего 8–16 регистров. Обращение к внешней памяти в RISC–процессорах используется только в операциях загрузки данных в РОН или пересылки результатов из РОН в память. За счет сокращения аппаратных средств, необходимых для декодирования и выполнения сложных команд, достигается существенное упрощение интегральных схем RISC–процессоров и снижение их стоимости. Кроме того, значительно повышается производительность. Благодаря указанным достоинствам во многих современных

CI SC –процессорах (последние модели Pentium и К7) используется RISC–ядро. При этом сложные CI SC–команды предварительно преобразуются в последовательность простых RISC–операций и быстро выполняются RISC–ядром;

? VLIW–архитектуру, которая относится к микропроцессорам с использованием очень длинных команд (Very Large Instruction Word— VLIW). Отдельные поля команды содержат коды, обеспечивающие выполнение различных операций. Одна VLIW –команда может выполнить сразу несколько операций одновременно в различных узлах микропроцессора. Формирование «длинных» VLIW – koманд производит соответствующий компилятор при трансляции программ, написанных на языке высокого уровня.

{xtypo_quote}VLIW –архитектура реализована в некоторых типах современных микропроцессоров и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров. {/xtypo_quote}

По способу организации выборки команд и данных различают два вида архитектур:

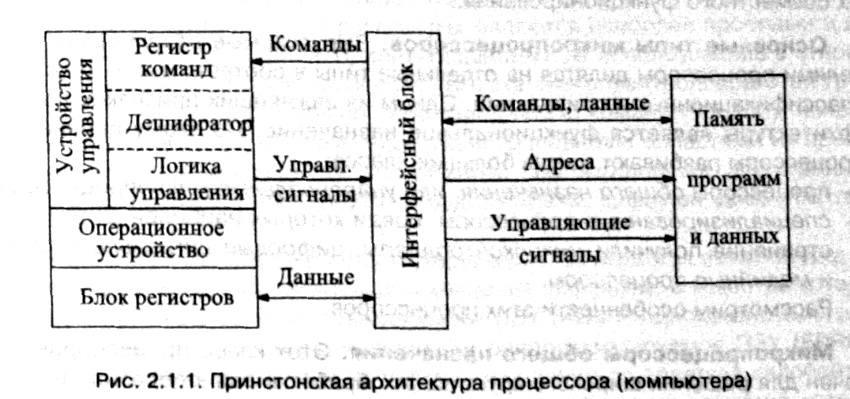

? принстонская архитектура, или архитектура фон–Неймана, особенностью которой является (рис. 2.1.1) использование:

• общей основной (оперативной) памяти для хранения программ и данных, что позволяет оперативно и эффективно перераспределять ее объем в зависимости от решаемых задач в каждом конкретном случае применении микропроцессора;

• общей шины, по которой в процессор поступают команды и данные, а в оперативную память записываются результаты, что значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Чтобы отделить команду от данных, первым из памяти всегда поступает код выполняемой операции, а затем следуют данные. По умолчанию код операции загружается в регистр команд, а данные — в блок регистров (рис. 2.1.1). Из–за ограниченного числа внешних выводов общая шина обычно работает в режиме временного мультиплексирования, т. е. противоположные направления обмена данными между микропроцессором, памятью или другими внешними устройствами разделены во времени.

Недостаток принстонской архитектуры

Использование общей шины для передачи команд и данных ограничивает производительность цифровой системы;

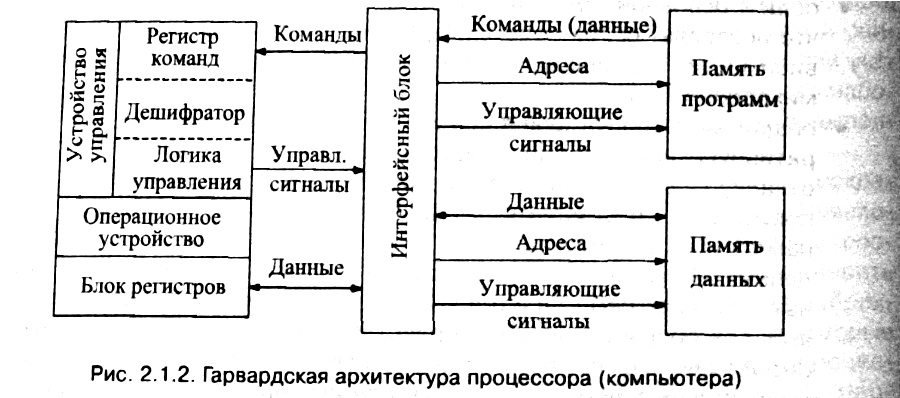

? гарвардская архитектура (создатель Говард Айкен), особенностью которой является физическое разделение памяти команд (программ) и памяти данных (рис. 2.1.2). Это обстоятельство вызвано постоянно возрастающими требованиями к производительности микропроцессорных систем. Память команд и память данных соединяются с процессором отдельными шинами. Благодаря разделению потоков команд и данных, а также совмещению операций их выборки (и записи результатов обработки) обеспечивается более высокая производительность, чем при использовании принстонской архитектуры.

Недостатки гарвардской архитектуры

Усложнение конструкции из–за использования отдельных шин для команд и данных; фиксированный объем памяти для команд и данных; увеличение общего объема памяти из–за невозможности ее оптимального перераспределения между командами и данными. Гарвардская архитектура получила широкое применение в микроконтроллерах — специализированных микропроцессорах для управления различными объектами, а также во внутренней структуре современных высокопроизводительных микропроцессоров в кэш–памяти с раздельным хранением команд и данных.

В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы принстонской архитектуры.

Отметим, что архитектура микропроцессора тесно связана с его структурой. Реализация тех или иных архитектурных особенностей требует введении в структуру микропроцессора соответствующих устройств и обеспечения механизмов их совместного функционирования.

onetwoclick.ru

onetwoclick.ru