При синхронном способе передачи каждый передаваемый бит данных сопровождается тактовым импульсом, под действием которого осуществляется синхронный сдвиг поступившего в сдвигающий регистр приемника бита. Передача начинается с пересылки в приемник одного или двух символов синхронизации в виде операндов. Эти символы информируют приемник о начале передачи. После этого в приемник пересылается предназначенный для передачи массив слов.

При синхронном способе передачи каждый передаваемый бит данных сопровождается тактовым импульсом, под действием которого осуществляется синхронный сдвиг поступившего в сдвигающий регистр приемника бита. Передача начинается с пересылки в приемник одного или двух символов синхронизации в виде операндов. Эти символы информируют приемник о начале передачи. После этого в приемник пересылается предназначенный для передачи массив слов.

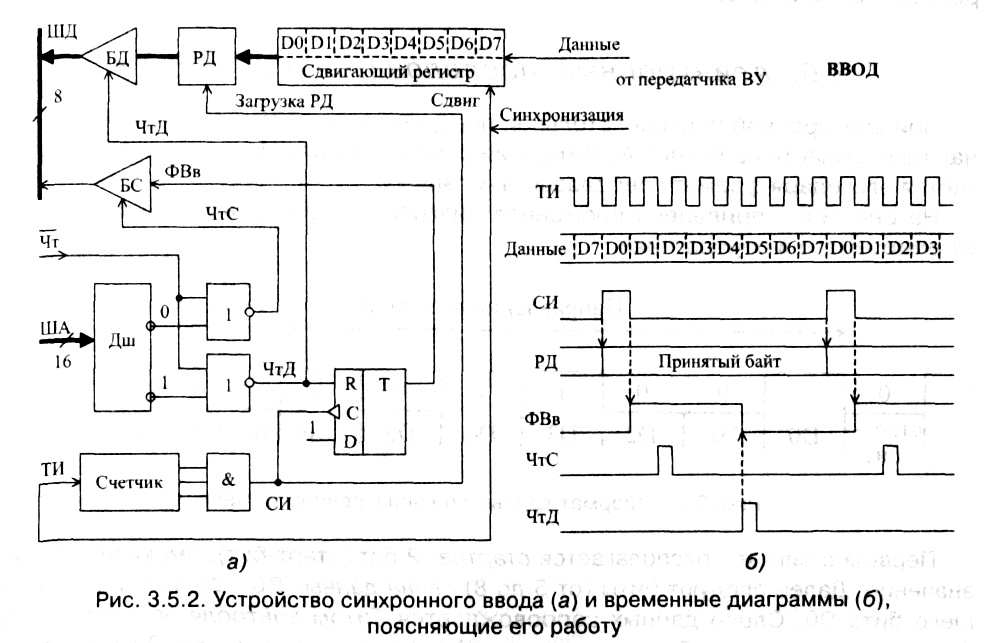

Вывод данных.

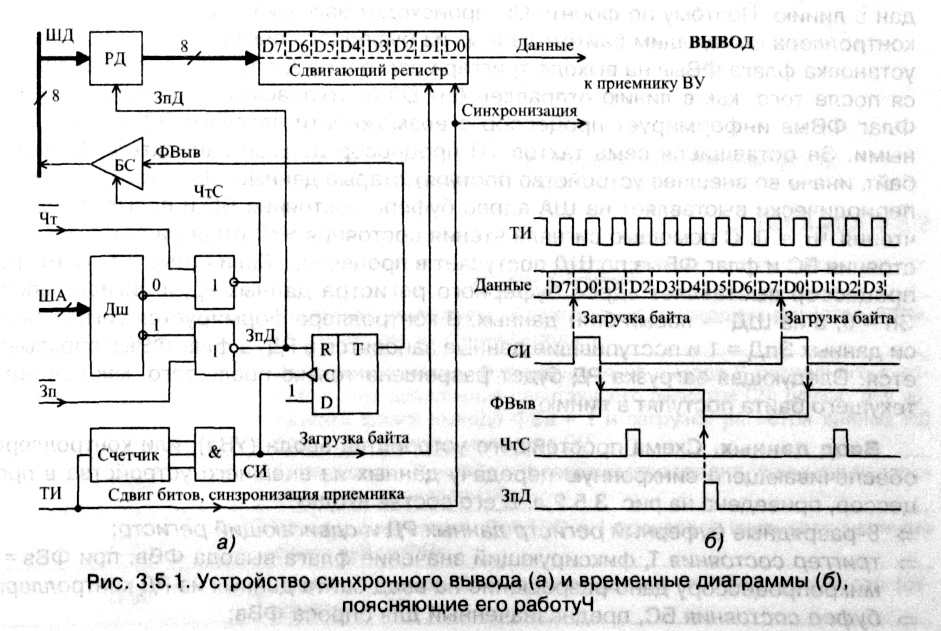

Схема простейшего устройства вывода (УВыв), или контроллера, обеспечивающего синхронную передачу данных во внешнее устройство, приведена на рис. 3.5.1, а. В его состав входят:

? 8–разрядные буферный регистр данных РД и сдвигающий регистр;

? триггер состояния

Т, фиксирующий значение флага вывода ФВыв: при ФВыв = 1 микропроцессору разрешается вывод байта данных в РД;

? буфер состояния

БС, предназначенный для опроса ФВыв;

? дешифратор

адреса Дш и логические элементы ИЛИ–НЕ, обеспечивающие доступ к триггеру состояния Т при опросе контроллера и к буферному регистру РД при записи байта данных;

? трехразрядный счетчик и элемент И, предназначенные для формирования синхроимпульсов СИ.

Назначение сигналов, используемых при выводе данных, приведено в табл. 3.5.1.

Для рассмотрения работы контроллера при передаче данных в ВУ воспользуемся временными диаграммами, приведенными на рис. 3.5.1, б.

Тактовые импульсы ТИ, поступая одновременно на сдвигающий регистр, счетчик и на выход контроллера для синхронизации приемника, выполняют следующие функции:

? осуществляют (по срезу ТИ) последовательную передачу бит (начиная с младшего) текущего слова из сдвигающего регистра в линию;

? формируют синхроимпульс СИ длительностью, равной периоду тактовых импульсов ТИ. Импульс формируется после каждого бита

D

7 с помощью счетчика, когда он находится в состоянии 111, и элемента И;

? синхронизируют сдвигающий регистр приемника ВУ, заполняя его принятыми битами данных.

Появление синхроимпульса СИ свидетельствует о том, что байт данных передан в линию. Поэтому по фронту СИ происходит загрузка сдвигающего регистра контроллера следующим байтом данных из буферного регистра РД, а по срезу — установка флага ФВыв на выходе триггера состояния Т, т. е. ФВыв устанавливается после того, как в линию отправлен бит

D

0 поступившего (очередного) байта. Флаг ФВыв информирует процессор о возможности загрузки РД новыми данными. За оставшиеся семь тактов ТИ процессор должен записать в РД новый байт, иначе во внешнее устройство поступят старые данные. Для этого процессор периодически выставляет на ША адрес буфера состояния БС и посылает сигнал чтения ?Чт = 0. С помощью сигнала чтения состояния ЧтС открывается буфер состояния БС и флаг ФВыв по ШД поступает в процессор. Если ФВыв = 1, то микропроцессор выставляет адрес буферного регистра данных РД и сигнал записи ?Зп = 0, а на ШД — новый байт данных. В контроллере формируется сигнал записи данных ЗпД = 1 и поступившие данные заносятся в РД, а флаг ФВыв сбрасывается. Следующая загрузка РД будет разрешена только после того, как все биты текущего байта поступят в линию.

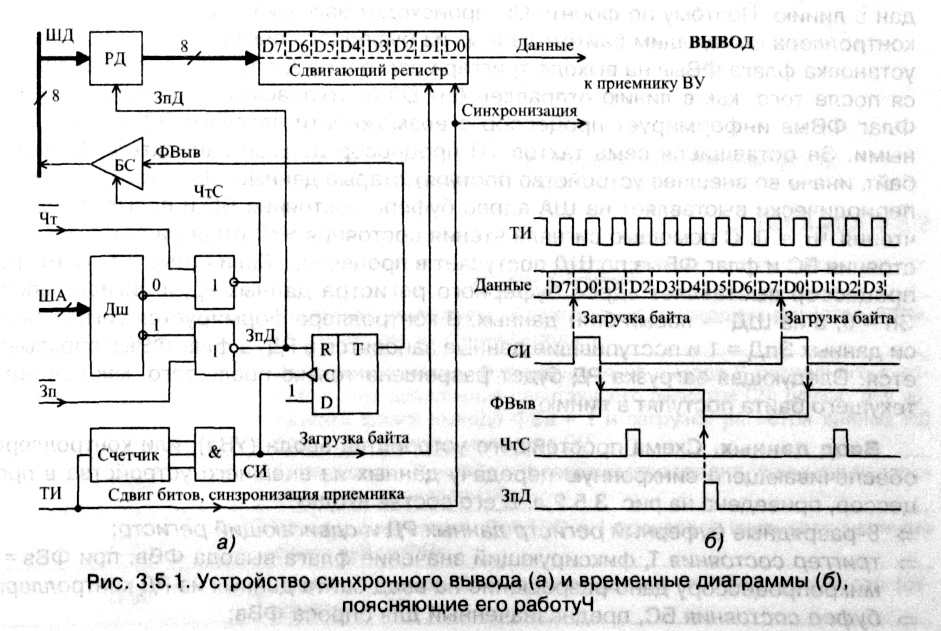

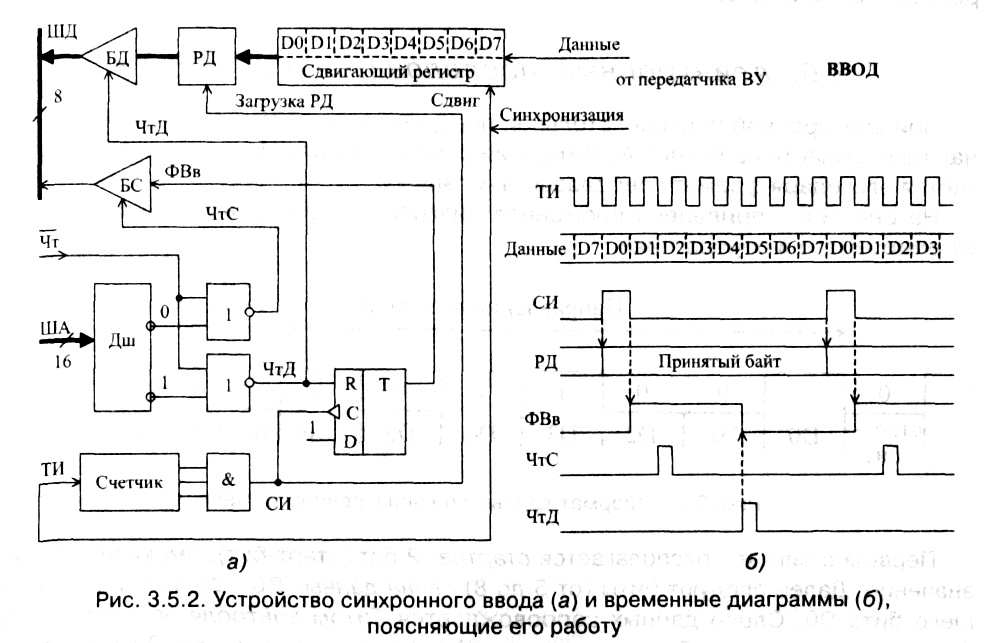

Ввод данных.

Схема простейшего устройства ввода (УВв), или контроллера, обеспечивающего синхронную передачу данных из внешнего устройства в процессор, приведена на рис. 3.5.2, а. В его состав входят:

? 8–разрядные буферный регистр данных РД и сдвигающий регистр;

? триггер состояния Т, фиксирующий значение флага вывода ФВв: при ФВв = 1 микропроцессору дано разрешение на ввод байта данных из РД контроллера;

? буфер состояния БС, предназначенный для опроса ФВв;

? дешифратор

адреса Дш и логические элементы ИЛИ–НЕ, обеспечивающие доступ к триггеру состояния Т при опросе и к буферному регистру РД при записи байта данных;

? трехразрядный счетчик и элемент И, предназначенные для формирования синхроимпульсов СИ.

Назначение сигналов, используемых при вводе данных, приведено в табл. 3.5.2.

Для рассмотрения работы контроллера при передаче данных из ВУ в процессор воспользуемся временными диаграммами, приведенными на рис. 3.5.2, б.

Тактовые импульсы ТИ, поступая из ВУ одновременно на сдвигающий регистр и трехразрядный счетчик, выполняют следующие функции:

? осуществляют (по срезу ТИ) последовательную загрузку сдвигающего регистра контроллера битами (начиная с младшего) текущего слова;

? формируют синхроимпульс СИ длительностью, равной периоду тактовых импульсов ТИ. Синхроимпульс формируется после каждого бита

D

7 с помощью счетчика, когда он находится в состоянии 111, и элемента И.

Появление синхроимпульса СИ свидетельствует о том, что байт данных принят из линии. Поэтому по фронту СИ принятый байт данных из сдвигающего регистра переписывается в регистр РД, а по срезу СИ устанавливается флаг ФВв на выходе триггера состояния Т, т. е. ФВв устанавливается после того, как принятый байт занесен в РД. Флаг ФВв = 1 информирует процессор о возможности ввода данных. За оставшиеся семь тактов ТИ микропроцессор должен считать из РД принятый байт, иначе он будет потерян, так как в РД поступят новые данные из ВУ. Для этого процессор периодически выставляет на ША адрес буфера состояния БС и посылает сигнал чтения ?Чт = 0. С помощью сигнала чтения состояния ЧтС открывается буфер состояния и флаг ФВв по ШД поступает в процессор. Если ФВв = 1, то процессор выставляет адрес регистра данных РД и сигнал записи ?Чт = 0. В контроллере формируется сигнал чтения данных ЧтД = 1 и поступившие данные через буфер БД выводятся из РД в процессор, а флаг ФВв сбрасывается. Следующий вывод из РД будет разрешен только после того, как в сдвигающий регистр поступит новый байт из линии.

Если ты хочешь отличного отдыха, проверенные феи в Чите, секс и удовольствие, то это на oopschita.ru. Да, вам совсем необязательно ехать куда-то, проститутки могут встретиться на вашей территории. Милые проверенные феи в Чите, страстные и желанные, они такие изобретательные и раскрепощённые, что ты не устоишь перед ними. Прелестницы ждут тебя.

onetwoclick.ru

onetwoclick.ru