Центральный процессор (ЦП), составленный из нескольких секций, служит основой микропроцессорного устройства (системы). Число используемых секций определяется требуемой разрядностью ЦП, т. е. разрядностью подлежащих обработке операндов.

Центральный процессор (ЦП), составленный из нескольких секций, служит основой микропроцессорного устройства (системы). Число используемых секций определяется требуемой разрядностью ЦП, т. е. разрядностью подлежащих обработке операндов.

Микропроцессорные устройства могут быть построены по принципу одноуровневого (микрокомандного) и двухуровневого (командно–микрокомандного) управления.

Для построения 4 m–разрядного ЦП число используемых секций должно составлять m. Объединение МПС осуществляется по следующим правилам:

- с помощью сигналов П0, П1 (обычно путем распайки) задается позиция каждой секции (П0 = 1, П1 = 0 — для секции младших разрядов; П0 = 0, П1 = 0 — для секций средних разрядов; П0 = 0, П1 = 1 или П0 = 1, П1 = 1 — для секции старших разрядов);

- входы синхроимпульсов (СИ) и приоритета (ПР), а также одноименные входы шины микрокоманд (ШМК) всех секций соединяются друг с другом;

- выходы переноса АЛУ (ПВых) и программного счетчика (ПСТВых) предыдущей секции соединяются соответственно с входами переноса АЛУ (П) и счетчика (ПСТ) следующей секции;

- выводы Л1, Л2 двунаправленных сдвигов одной секции соединяются соответственно с выводами П1, П2 соседней секции;

- ШВх, ШВых, ШАдр всех секций объединяются, образуя входные, выходные и адресные 4 m–разрядные шины ЦП;

- на выводы П, ПСТ, УИ/СтА секции младших разрядов подаются соответственно входные сигналы переноса АЛУ, программного счетчика и управления инкрементором; с вывода ДРО/ДРЗ снимается бит младшего разряда дополнительного регистра;

- выводы ДРО/ДРЗ, УИ/СтА, ПСТВых/СтВ секции старших разрядов служат для получения информации о значении старших разрядов 4 m–разрядных операндов рабочего регистра, мультиплексоров А и В; сигнал ПВых старшей секции фиксирует переполнение ЦП.

Если для повышения быстродействия ЦП используется блок ускоренного переноса (БУП), то выходы генерации (G) и переноса (Р) каждой секции соединены с одноименными входами указанного блока; сигналы С, на входы переноса АЛУ (П) всех секций, за исключением секции младших разрядов, поступают с блока ускоренного переноса.

На рис. 1.6.3 в качестве примера приведена схема 16–разрядного ЦП, составленного из четырех МПС.

Двухуровневое микропроцессорное устройство

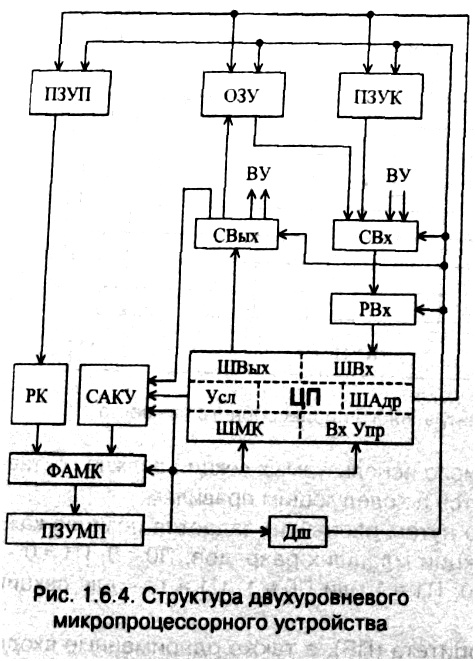

На рис. 1.6.4 изображена структурная схема микропроцессорного устройства, построенного по принципу командно–микрокомандного управления.

Устройство содержит следующие узлы:

- центральный процессор ЦП, составленный из нескольких МПС;

- ОЗУ, ПЗУ констант (ПЗУК), ПЗУ программ (ПЗУП) и ПЗУ микропрограмм (ПЗУМП);

- регистр команд (РК) для хранения кода команд на время их исполнения и входной регистр (РВх) для фиксации данных, поступающих на ШВх;

- схему анализа и коммутатор условий (САКУ), предназначенные для формирования признаков результата (знак, нулевое значение и др.) на основе анализа данных, поступающих с ШВых, и выбора условия, поступающего в виде сигналов ДР0, ДРЗ, СтА, СтВ, ПВых с выходов Усл ЦП;

- формирователь адресов микрокоманд (ФАМК), вырабатывающий на каждом такте адрес следующий микрокоманды;

- дешифратор кода микрокоманды (ДШКМК), вырабатывающий управляющие сигналы для отдельных узлов устройства;

- селекторы входа (СВх) и выхода (СВых), предназначенные для подключений соответственно ШВх и ШВых ЦП к одному из внутренних узлов (ОЗУ, ПЗУ констант, САКУ) или внешним устройствам (ВУ).

Рассмотрим работу устройства при выполнении программы. Адрес очередной команды задается программным счетчиком ЦП. Считываемый по этому адресу из ПЗУП код команды заносится на время ее исполнения в РК. Код команды задает начальный адрес микропрограммы выполняемой операции, т. е. адрес первой микрокоманды микропрограммы. Узлы устройства выполняют инструкции, содержащиеся в формате микрокоманды, считываемой из ПЗУМП на каждом такте. Результаты выполнения каждой микрокоманды поступают на ШВых ЦП и через СВых передаются в ОЗУ, САКУ или ВУ. Адреса последующих микрокоманд микропрограммы вырабатываются в ФАМК на основе информации, поступающей из САКУ и ПЗУМП. По завершении выполнения текущей микропрограммы начинается выборка кода для выполнения следующей команды.

Программируемые процессоры

Такие процессоры используют программирование на языке команд. Все современные процессоры относятся к этому типу. Для программируемых процессоров, или просто процессоров, отсутствует регулярная структура. Программируемый процессор может быть построен по двухуровневой схеме (рис. 1.6.4) на основе микропрограммируемого процессора.

Приведем некоторые сведения, необходимые для ознакомления с особенностями программируемых процессоров.

На процессор возлагается выполнение таких функций, как:

- выборка команд из внешней памяти, их дешифрация и выполнение;

- прием данных из внешней (основной) памяти, выполнение над ними арифметических, логических и других операций (из заданного набора), определяемых кодом команды, и передача обработанных данных во внешние устройства или память;

- формирование сигналов состояния, управления и времени, необходимых для нормальной работы внутренних узлов, а также внешних устройств и памяти;

- реагирование на внешние сигналы и обслуживание запросов внешних устройств.

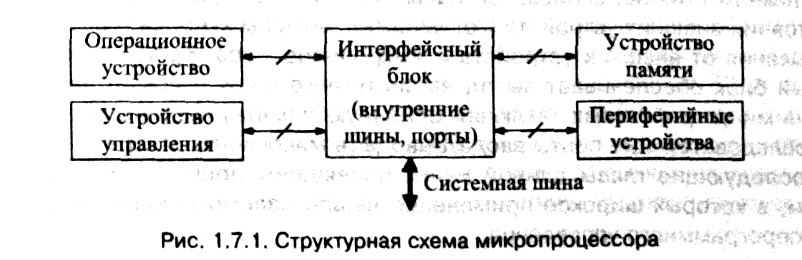

Исходя из возлагаемых на процессор функций, его можно представить как совокупности следующих основных функциональных блоков (устройств), показанных на рис. 1.7.1:

- операционное устройство, выполняющее определенный набор команд (инструкций): команды пересылки данных; команды арифметических, логических и битовых операций; команды безусловной передачи управления и условных переходов; команды организации программных циклов и др. Набор команд современных универсальных процессоров насчитывает несколько сотен инструкций. Основу операционного автомата простейших микропроцессоров составляет арифметическо–логическое устройство (АЛУ), которое в большинстве случаев:

- состоит из двоичного сумматора со схемами ускоренного переноса, регистров для временного хранения операндов и регистра – сдвигателя, комбинационных схем для выработки логических условий и работы с десятичной арифметикой;

- выполняет операции арифметического сложения и вычитания, пересылки, логического И и ИЛИ, инверсии, сложения по модулю 2, сдвига и др. Современные микропроцессоры могут содержать дополнительные функциональные узлы (например, для операций с плавающей точкой), операционные блоки (модули) для параллельной обработки информации и др.;

- устройство управления, основные функции которого состоят в управлении процессом выполнения команд, а именно, в формировании требуемой последовательности управляющих сигналов (микрокоманд, выполняемых на одном процессорном такте).

Совокупность микрокоманд (микрокод) хранится в постоянной памяти.

Требуемая последовательность микрокоманд формируется после дешифрации команды. При выполнении отдельных микрокоманд используются осведомительные сигналы (логические условия, признаки, флаги), поступающие со стороны операционного устройства. Осведомительные сигналы информируют устройство управления о состоянии операционного устройства. Устройство управления строится на основе программируемой и (или) схемной логики. В его состав могут входить регистр и дешифратор команд, генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других узлов;

- устройство памяти в виде набора регистров, образующих внутреннюю память процессора. Часть регистров доступна программисту и предназначена для хранения операндов, выполнения действий над ними и обращения (адресации) к внешней по отношение к микропроцессору памяти. Хранение во внутренних регистрах операндов значительно ускоряет выполнение программы, так как отсутствует необходимость обращения к основной памяти по внешней шине (магистрали), которое требует дополнительного времени (отдельного машинного цикла). Другая часть регистров, доступ к которым может быть ограничен и даже исключен (программно–невидимые регистры), используется процессором для служебных (системных) целей. Помимо регистров устройство памяти может содержать модули оперативной и постоянной памяти, один или два уровня кэш–памяти, предназначенной для ускорения доступа к внешней памяти;

- периферийные устройства, к которым относятся специализированные контроллеры, аналого–цифровые преобразователи, таймерные модули и др.;

- интерфейсный блок, обеспечивающий связь (взаимодействие) между внутренними устройствами и узлами, которая осуществляется по многоразрядным шинам.

По функциональному назначению различают шину данных, шину адреса и шину управления.

Внутренняя шина данных соединяет между собой АЛУ, устройство управления, блок регистров общего назначения, регистр адреса. Шина адреса предназначена для обращения к ячейкам внешней памяти и определяет их число. Например, 16–разрядная адресная шина позволяет прямо адресовать 216 = 64К ячеек памяти, где К = 210 = 1024. Двунаправленная шина управления обычно служит для передачи управляющих сигналов, признаков состояния процессора и периферийного оборудования. По ней передаются: синхронизирующие сигналы; сигналы обращения к памяти (чтение, запись); сигналы, информирующие микропроцессор о состоянии внешних устройств (готовность); сигналы запроса и разрешения прерывания от внешних устройств и микропроцессора. Кроме того, интерфейсный блок обеспечивает выход на системную шину и обмен данными с внешними устройствами (включая основную память) через параллельные или последовательные порты ввода/вывода (в микроконтроллерах).

Встречаются в свободное время и в своё удовольствие, феи Борзя избирательны во встречах, поэтому просьба о свидании договариваться заранее. Умелая путаны подарят вам массу ярких ощущений, доведя до исступления. Стильные феи Борзя, пылкие и страстные, они такие изобретательные и молоденькие, что у любого появится желание. Твои мечты и желания реализуются.

onetwoclick.ru

onetwoclick.ru